MPC9350

Rev 6, 4/2005

Freescale Semiconductor

Technical Data

Low Voltage PLL Clock Driver

MPC9350

The MPC9350 is a 2.5 V and 3.3 V compatible, PLL-based clock generator

targeted for high performance clock distribution systems. With output

frequencies of up to 200 MHz and maximum output skews of 150 ps, the

MPC9350 is ideal for the most demanding clock tree designs. The device offers

9 low skew clock outputs, with each one configurable to support the clocking

needs of the various high-performance microprocessors, including the

PowerQUICC II integrated communication microprocessor. The extended

temperature range of the MPC9350 supports telecommunication and networking

requirements. The device employs a fully differential PLL design to minimize

cycle-to-cycle and long-term jitter.

LOW VOLTAGE

3.3 V AND 2.5 V PLL

CLOCK GENERATOR

Features

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

9 output LVCMOS PLL clock generator

25 – 200 MHz output frequency range

2.5 V and 3.3 V compatible

FA SUFFIX

32-LEAD LQFP PACKAGE

CASE 873A-03

Compatible to various microprocessors such as PowerQuicc II

Supports networking, telecommunications and computer applications

Fully integrated PLL

Configurable outputs: divide-by-2, 4 and 8 of VCO frequency

Selectable output to input frequency ratio of 8:1, 4:1, 2:1 or 1:1

Oscillator or crystal reference inputs

Internal PLL feedback

AC SUFFIX

32-LEAD LQFP PACKAGE

Pb-FREE PACKAGE

CASE 873A-03

Output disable

PLL enable/disable

Low skew characteristics: maximum 150 ps output-to-output

32-lead LQFP package

32-lead Pb-free Package Available

Temperature range –40°C to +85°C

Functional Description

The MPC9350 generates high frequency clock signals and provides nine exact frequency-multiplied copies of the reference

clock signal. The internal PLL allows the MPC9350 to operate in frequency locked condition and to multiply the input reference

clock. The reference clock frequency and the divider in the internal feedback path determine the VCO frequency. Two selectable

PLL feedback frequency ratios are available on the MPC9350 to provide input frequency range flexibility. The FBSEL pin selects

between divide-by-16 or divide-by-32 of the VCO frequency for PLL feedback. This feedback divider must be selected to match

the VCO frequency range. With the available feedback output dividers, the internal VCO of the MPC9350 is running at either 16x

or 32x of the reference clock frequency. The frequency of the QA, QB, QC and QD outputs is either one half, one fourth or one

eighth of the selected VCO frequency and can be configured for each output bank using the FSELA, FSELB, FSELC and FSELD

pins, respectively. The available output to input frequency ratios are 16:1, 8:1, 4:1 and 2:1. The REF_SEL pin selects the crystal

oscillator input or the LVCMOS compatible reference input (TCLK). TCLK also provides an external test clock in static test mode

when the PLL enable pin (PLL_EN) is pulled to logic low state. In test mode, the selected input reference clock is routed directly

to the output dividers without using the PLL. The test mode is intended for system diagnostics, test and debug purposes. This

test mode is fully static and the minimum clock frequency specification does not apply. The outputs can be disabled by

deasserting the OE pin (logic high state). In PLL mode, deasserting OE maintains PLL lock due to the internal feedback path.

The MPC9350 is fully 2.5 V and 3.3 V compatible and requires no external loop filter components. The on-chip crystal oscillator

requires no external components beyond a series resonant crystal. All inputs except the crystal oscillator interface accept

LVCMOS signals while the outputs provide LVCMOS compatible levels with the capability to drive terminated 50 Ω transmission

lines. For series terminated transmission lines, each of the MPC9350 outputs can drive one or two traces giving the device an

effective fanout of 1:18. The device is packaged in a 7x7 mm2 32-lead LQFP package.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

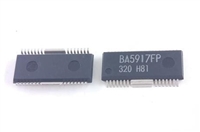

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐