| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| NB3W1900L_18 | ONSEMI |

获取价格 |

Differential 1:19 HCSL-Compatible PushâPull |

|

| NB3W1900LMNG | ONSEMI |

获取价格 |

Differential 1:19 HCSL-Compatible PushâPull |

|

| NB3W1900LMNTXG | ONSEMI |

获取价格 |

Differential 1:19 HCSL-Compatible PushâPull |

|

| NB3W800L | ONSEMI |

获取价格 |

Differential 1:8 HCSLCompatible Push-Pull Clock |

|

| NB3W800L_16 | ONSEMI |

获取价格 |

Differential 1:8 HCSLCompatible Push-Pull Clock |

|

| NB3W800L_17 | ONSEMI |

获取价格 |

Differential 1:8 HCSLCompatible Push-Pull Clock |

|

| NB3W800LMNG | ONSEMI |

获取价格 |

Differential 1:8 HCSLCompatible Push-Pull Clock |

|

| NB3W800LMNTWG | ONSEMI |

获取价格 |

Differential 1:8 HCSLCompatible Push-Pull Clock |

|

| NB3W800LMNTXG | ONSEMI |

获取价格 |

Differential 1:8 HCSLCompatible Push-Pull Clock |

|

| NB4 | GLENAIR |

获取价格 |

Military Standard Connector Index |

|

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

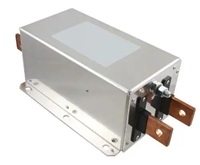

网络滤波器、EMI滤波器与EMC滤波器在电子元器件中的分类关系

网络滤波器、EMI滤波器与EMC滤波器在电子元器件中的分类关系

NTC热敏电阻与PTC热敏电阻的应用原理及选型原则

NTC热敏电阻与PTC热敏电阻的应用原理及选型原则