| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| SN74SSTV16859_16 | TI |

获取价格 |

3-BIT TO 26-BIT REGISTERED BUFFER WITH SSTL 2 INPUTS AND OUTPUTS |

|

| SN74SSTV16859DGG | TI |

获取价格 |

13-Bit to 26-Bit Registered Buffer with SSTL_2 Inputs and Outputs 64-TSSOP |

|

| SN74SSTV16859DGGG4 | TI |

获取价格 |

13-Bit to 26-Bit Registered Buffer with SSTL_2 Inputs and Outputs 64-TSSOP |

|

| SN74SSTV16859DGGR | TI |

获取价格 |

13-BIT TO 26-BIT REGISTERED BUFFER WITH SSTL 2 INPUTS AND OUTPUTS |

|

| SN74SSTV16859RGQ8 | TI |

获取价格 |

13-BIT TO 26-BIT REGISTERED BUFFER WITH SSTL 2 INPUTS AND OUTPUTS |

|

| SN74SSTV16859RGQR | TI |

获取价格 |

13-BIT TO 26-BIT REGISTERED BUFFER WITH SSTL 2 INPUTS AND OUTPUTS |

|

| SN74SSTV32852 | TI |

获取价格 |

24-BIT TO 48-BIT REGISTERED BUFFER WITH SSTL_2 INPUTS AND OUTPUTS |

|

| SN74SSTV32852_09 | TI |

获取价格 |

24-BIT TO 48-BIT REGISTERED BUFFER WITH SSTL_2 INPUTS AND OUTPUTS |

|

| SN74SSTV32852-EP | TI |

获取价格 |

24-BIT TO 48-BIT REGISTERED BUFFER WITH SSTL_2 INPUTS AND OUTPUTS |

|

| SN74SSTV32852GKFR | TI |

获取价格 |

24-BIT TO 48-BIT REGISTERED BUFFER WITH SSTL_2 INPUTS AND OUTPUTS |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

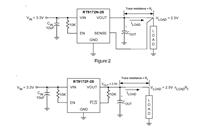

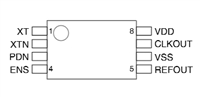

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征