| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| ICS86004G-01T | IDT | PLL Based Clock Driver, 86004 Series, 4 True Output(s), 0 Inverted Output(s), PDSO16, 4.40 |

获取价格 |

|

| ICS8602 | ICSI | ZERO DELAY, DIFFERENTIAL-TO-LVCMOS/LVTTL |

获取价格 |

|

| ICS8602AYLF | IDT | Low Skew Clock Driver, 9 True Output(s), 0 Inverted Output(s), CMOS, PQFP32, 7 X 7 MM, 1.4 |

获取价格 |

|

| ICS8602AYLFT | IDT | Low Skew Clock Driver, 9 True Output(s), 0 Inverted Output(s), CMOS, PQFP32, 7 X 7 MM, 1.4 |

获取价格 |

|

| ICS8602AYT | IDT | Low Skew Clock Driver, 9 True Output(s), 0 Inverted Output(s), CMOS, PQFP32, 7 X 7 MM, 1.4 |

获取价格 |

|

| ICS8602BT | ICSI | ZERO DELAY, DIFFERENTIAL-TO-LVCMOS/LVTTL |

获取价格 |

|

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

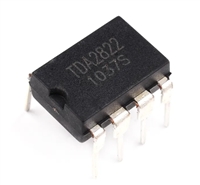

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍