| 是否Rohs认证: | 符合 | 生命周期: | Transferred |

| 零件包装代码: | SOP | 包装说明: | 3.90 MM, PLASTIC, MS-012, SOT109-1, SOP-16 |

| 针数: | 16 | Reach Compliance Code: | compliant |

| ECCN代码: | EAR99 | HTS代码: | 8542.39.00.01 |

| 风险等级: | 6.9 | Is Samacsys: | N |

| 其他特性: | 3 ENABLE INPUTS | 系列: | HC/UH |

| 输入调节: | STANDARD | JESD-30 代码: | R-PDSO-G16 |

| 长度: | 9.9 mm | 负载电容(CL): | 50 pF |

| 逻辑集成电路类型: | OTHER DECODER/DRIVER | 最大I(ol): | 0.004 A |

| 湿度敏感等级: | 1 | 功能数量: | 1 |

| 端子数量: | 16 | 最高工作温度: | 125 °C |

| 最低工作温度: | -40 °C | 输出极性: | INVERTED |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | SOP |

| 封装等效代码: | SOP16,.25 | 封装形状: | RECTANGULAR |

| 封装形式: | SMALL OUTLINE | 包装方法: | TUBE |

| 峰值回流温度(摄氏度): | 260 | 电源: | 2/6 V |

| Prop。Delay @ Nom-Sup: | 45 ns | 传播延迟(tpd): | 225 ns |

| 认证状态: | Not Qualified | 座面最大高度: | 1.75 mm |

| 子类别: | Decoder/Drivers | 最大供电电压 (Vsup): | 6 V |

| 最小供电电压 (Vsup): | 2 V | 标称供电电压 (Vsup): | 5 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | AUTOMOTIVE | 端子面层: | NICKEL/PALLADIUM/GOLD (NI/PD/AU) |

| 端子形式: | GULL WING | 端子节距: | 1.27 mm |

| 端子位置: | DUAL | 处于峰值回流温度下的最长时间: | 30 |

| 宽度: | 3.9 mm | Base Number Matches: | 1 |

| 型号 | 品牌 | 替代类型 | 描述 | 数据表 |

| 74HC138D,653 | NXP |

完全替代  |

74HC(T)138 - 3-to-8 line decoder/demultiplexer; inverting SOP 16-Pin |

|

| MC74HC138ADG | ONSEMI |

功能相似  |

1−of−8 Decoder/ Demultiplexer |

|

| MC74HC138ADR2G | ONSEMI |

功能相似  |

1−of−8 Decoder/ Demultiplexer |

|

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74HC138D,653 | NXP |

获取价格 |

74HC(T)138 - 3-to-8 line decoder/demultiplexer; inverting SOP 16-Pin |

|

| 74HC138D,653 | NEXPERIA |

获取价格 |

元器件封装:16-SOIC; |

|

| 74HC138D-Q100 | NXP |

获取价格 |

3-to-8 line decoder/demultiplexer; inverting |

|

| 74HC138D-Q100 | NEXPERIA |

获取价格 |

3-to-8 line decoder/demultiplexer; invertingProduction |

|

| 74HC138D-Q100,118 | NEXPERIA |

获取价格 |

元器件封装:16-SO; |

|

| 74HC138D-Q100HL | NEXPERIA |

获取价格 |

IC DECODER/DEMUX 3 TO 8 16SOIC |

|

| 74HC138D-T | NXP |

获取价格 |

HC/UH SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDSO16, 3.90 MM, PLASTIC, MS-012, SOT |

|

| 74HC138DB | NXP |

获取价格 |

3-to-8 line decoder/demultiplexer; inverting |

|

| 74HC138DB | NEXPERIA |

获取价格 |

3-to-8 line decoder/demultiplexer; inverting |

|

| 74HC138DB,112 | NEXPERIA |

获取价格 |

元器件封装:16-SSOP; |

|

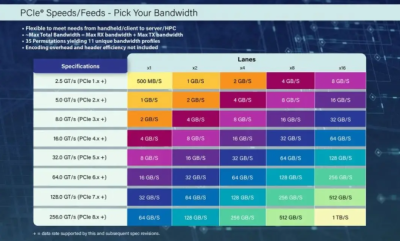

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

闪迪预警:NAND闪存供应短缺将持续至2026年

闪迪预警:NAND闪存供应短缺将持续至2026年