| 是否Rohs认证: | 符合 | 生命周期: | Transferred |

| 零件包装代码: | QFN | 包装说明: | 2.50 X 3.50 MM, 0.85 MM HEIGHT, PLASTIC, MO-241, SOT763-1, DHVQFN-16 |

| 针数: | 16 | Reach Compliance Code: | compliant |

| 风险等级: | 5.75 | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74HC138D | NXP |

获取价格 |

3-to-8 line decoder/demultiplexer; inverting |

|

| 74HC138D | NEXPERIA |

获取价格 |

3-to-8 line decoder/demultiplexer; invertingProduction |

|

| 74HC138D | TOSHIBA |

获取价格 |

3-to-8 Line Decoder, SOIC16 |

|

| 74HC138D,652 | NXP |

获取价格 |

74HC(T)138 - 3-to-8 line decoder/demultiplexer; inverting SOP 16-Pin |

|

| 74HC138D,653 | NXP |

获取价格 |

74HC(T)138 - 3-to-8 line decoder/demultiplexer; inverting SOP 16-Pin |

|

| 74HC138D,653 | NEXPERIA |

获取价格 |

元器件封装:16-SOIC; |

|

| 74HC138D-Q100 | NXP |

获取价格 |

3-to-8 line decoder/demultiplexer; inverting |

|

| 74HC138D-Q100 | NEXPERIA |

获取价格 |

3-to-8 line decoder/demultiplexer; invertingProduction |

|

| 74HC138D-Q100,118 | NEXPERIA |

获取价格 |

元器件封装:16-SO; |

|

| 74HC138D-Q100HL | NEXPERIA |

获取价格 |

IC DECODER/DEMUX 3 TO 8 16SOIC |

|

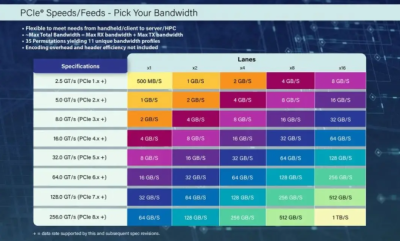

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

闪迪预警:NAND闪存供应短缺将持续至2026年

闪迪预警:NAND闪存供应短缺将持续至2026年