| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| MC100EP139DT | ONSEMI |

获取价格 |

±2/4, ±4./5/6 Clock Generation Chip |

|

| MC100EP139DTG | ONSEMI |

获取价格 |

3.3V / 5V ECL ±2/4, ±4/5/6 Clock Generation C |

|

| MC100EP139DTR2 | ONSEMI |

获取价格 |

±2/4, ±4./5/6 Clock Generation Chip |

|

| MC100EP139DTR2G | ONSEMI |

获取价格 |

3.3V / 5V ECL ±2/4, ±4/5/6 Clock Generation C |

|

| MC100EP139DW | ONSEMI |

获取价格 |

±2/4, ±4./5/6 Clock Generation Chip |

|

| MC100EP139DWG | ONSEMI |

获取价格 |

3.3V / 5V ECL ±2/4, ±4/5/6 Clock Generation C |

|

| MC100EP139DWR2 | ONSEMI |

获取价格 |

±2/4, ±4./5/6 Clock Generation Chip |

|

| MC100EP139DWR2G | ONSEMI |

获取价格 |

3.3V / 5V ECL ±2/4, ±4/5/6 Clock Generation C |

|

| MC100EP139MNG | ONSEMI |

获取价格 |

3.3V / 5V ECL ±2/4, ±4/5/6 Clock Generation C |

|

| MC100EP139MNTXG | ONSEMI |

获取价格 |

3.3V / 5V ECL ±2/4, ±4/5/6 Clock Generation C |

|

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

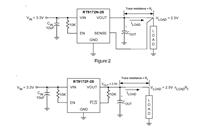

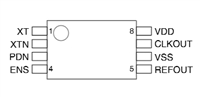

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征

解读MAX3238ECPW:一款多通道RS-232线驱动/接收器

解读MAX3238ECPW:一款多通道RS-232线驱动/接收器