| Source Url Status Check Date: | 2013-06-14 00:00:00 | 是否Rohs认证: | 符合 |

| 生命周期: | Obsolete | 零件包装代码: | TSSOP |

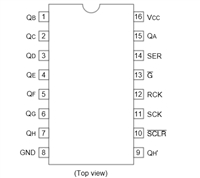

| 包装说明: | 4.40 MM, PLASTIC, MO-153, SOT-403-1, TSSOP-16 | 针数: | 16 |

| Reach Compliance Code: | unknown | HTS代码: | 8542.39.00.01 |

| 风险等级: | 5.08 | Is Samacsys: | N |

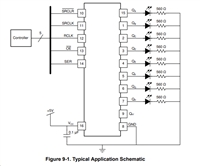

| 其他特性: | SERIAL STANDARD OUTPUT FOR CASCADING | 计数方向: | RIGHT |

| 系列: | HC/UH | JESD-30 代码: | R-PDSO-G16 |

| JESD-609代码: | e4 | 长度: | 5 mm |

| 逻辑集成电路类型: | SERIAL IN PARALLEL OUT | 湿度敏感等级: | 1 |

| 位数: | 8 | 功能数量: | 1 |

| 端子数量: | 16 | 最高工作温度: | 125 °C |

| 最低工作温度: | -40 °C | 输出特性: | 3-STATE |

| 输出极性: | TRUE | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | TSSOP | 封装形状: | RECTANGULAR |

| 封装形式: | SMALL OUTLINE, THIN PROFILE, SHRINK PITCH | 峰值回流温度(摄氏度): | 260 |

| 传播延迟(tpd): | 265 ns | 认证状态: | Not Qualified |

| 座面最大高度: | 1.1 mm | 最大供电电压 (Vsup): | 6 V |

| 最小供电电压 (Vsup): | 2 V | 标称供电电压 (Vsup): | 5 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | AUTOMOTIVE | 端子面层: | NICKEL PALLADIUM GOLD |

| 端子形式: | GULL WING | 端子节距: | 0.65 mm |

| 端子位置: | DUAL | 处于峰值回流温度下的最长时间: | 30 |

| 触发器类型: | POSITIVE EDGE | 宽度: | 4.4 mm |

| 最小 fmax: | 24 MHz | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74HC595-50 | HGSEMI |

获取价格 |

8位CMOS 移位寄存器, 驱动电流:50mA |

|

| 74HC595BQ | NXP |

获取价格 |

8-bit serial-in/serial or parallel-out shift register with output latches; 3-state |

|

| 74HC595BQ | NEXPERIA |

获取价格 |

8-bit serial-in, serial or parallel-out shift |

|

| 74HC595BQ115 | NXP |

获取价格 |

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state |

|

| 74HC595BQ-Q100 | NXP |

获取价格 |

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state |

|

| 74HC595BQ-Q100 | NEXPERIA |

获取价格 |

8-bit serial-in, serial or parallel-out shift |

|

| 74HC595BQ-Q100,115 | NXP |

获取价格 |

74HC(T)595-Q100 - 8-bit serial-in, serial or parallel-out shift register with output latch |

|

| 74HC595BZ | NEXPERIA |

获取价格 |

8-bit serial-in, serial or parallel-out shift |

|

| 74HC595D | NEXPERIA |

获取价格 |

8-bit serial-in, serial or parallel-out shift |

|

| 74HC595D | NXP |

获取价格 |

8-bit serial-in/serial or parallel-out shift register with output latches; 3-state |

|

74HC595D芯片引脚图及功能、参数介绍、替代型号推荐

74HC595D芯片引脚图及功能、参数介绍、替代型号推荐

74HC595移位寄存器芯片:参数深入解析与应用实践指南

74HC595移位寄存器芯片:参数深入解析与应用实践指南

74HC595芯片工作原理以及应用分析

74HC595芯片工作原理以及应用分析

数码管:基本概念、分类、技术发展及市场趋势

数码管:基本概念、分类、技术发展及市场趋势