| 型号 | 品牌 | 替代类型 | 描述 | 数据表 |

| CY62148ELL-45SXI | CYPRESS |

功能相似  |

Standard SRAM, 512KX8, 45ns, CMOS, PDSO32, 0.450 INCH, LEAD FREE, SOIC-32 |

|

| CY62148BLL-70SC | CYPRESS |

功能相似  |

512K x 8 Static RAM |

|

| TC554001AF-70L | TOSHIBA |

功能相似  |

524,228 WORDS x 8 BIT STATIC RAM |

|

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CY62148BNLL-70SXCT | CYPRESS |

获取价格 |

暂无描述 |

|

| CY62148BNLL-70SXI | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNLL-70SXIT | CYPRESS |

获取价格 |

Standard SRAM, 512KX8, 70ns, CMOS, PDSO32, |

|

| CY62148BNLL-70ZC | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNLL-70ZI | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNLL-70ZRC | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNLL-70ZRI | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNLL-70ZXC | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNLL-70ZXI | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

| CY62148BNSL-70SXI | CYPRESS |

获取价格 |

4-Mbit (512K x 8) Static RAM |

|

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

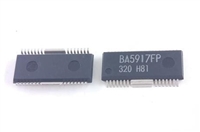

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐