| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CMN1003GXP | APPLIED POWER |

获取价格 |

TO-220 |

|

| CMN1005GF5 | APPLIED POWER |

获取价格 |

DFN5x6 |

|

| CMN10080GRD | APPLIED POWER |

获取价格 |

TO-251 |

|

| CMN10080GRU | APPLIED POWER |

获取价格 |

TO-252 |

|

| CMN1008LGXF5 | APPLIED POWER |

获取价格 |

DFN5x6 |

|

| CMN10090TD | APPLIED POWER |

获取价格 |

TO-251 |

|

| CMN10090TF3 | APPLIED POWER |

获取价格 |

PDFN3.3x3.3 |

|

| CMN10090TU | APPLIED POWER |

获取价格 |

TO-252 |

|

| CMN10098GSS3 | APPLIED POWER |

获取价格 |

SOT-223 |

|

| CMN100A0GSD | APPLIED POWER |

获取价格 |

TO-251 |

|

英伟达驱动支持期限敲定:Maxwell/Pascal/Volta架构仅剩最后一年

英伟达驱动支持期限敲定:Maxwell/Pascal/Volta架构仅剩最后一年

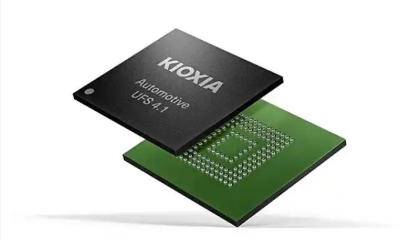

铠侠车用UFS 4.1闪存发布:性能飙升3.7倍,1TB容量改写车载存储格局

铠侠车用UFS 4.1闪存发布:性能飙升3.7倍,1TB容量改写车载存储格局

三星抢跑2纳米时代!Exynos 2600芯片或成Galaxy S26杀手锏

三星抢跑2纳米时代!Exynos 2600芯片或成Galaxy S26杀手锏

铠侠车规级UFS 4.1震撼发布:随机写入速度飙升至3.7倍

铠侠车规级UFS 4.1震撼发布:随机写入速度飙升至3.7倍