| 是否Rohs认证: | 符合 | 生命周期: | Active |

| 零件包装代码: | QFN | 包装说明: | HVQCCN, |

| 针数: | 20 | Reach Compliance Code: | compliant |

| HTS代码: | 8542.39.00.01 | 风险等级: | 1.06 |

| Samacsys Confidence: | 2 | Samacsys Status: | Released |

| Samacsys PartID: | 1432571 | Samacsys Pin Count: | 21 |

| Samacsys Part Category: | Integrated Circuit | Samacsys Package Category: | Other |

| Samacsys Footprint Name: | DHVQFN20 (SOT764-1) | Samacsys Released Date: | 2019-11-12 07:41:52 |

| Is Samacsys: | N | 系列: | LVC/LCX/Z |

| JESD-30 代码: | R-PQCC-N20 | JESD-609代码: | e4 |

| 长度: | 4.5 mm | 逻辑集成电路类型: | BUS DRIVER |

| 湿度敏感等级: | 1 | 位数: | 8 |

| 功能数量: | 1 | 端口数量: | 2 |

| 端子数量: | 20 | 最高工作温度: | 125 °C |

| 最低工作温度: | -40 °C | 输出特性: | 3-STATE |

| 输出极性: | TRUE | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | HVQCCN | 封装形状: | RECTANGULAR |

| 封装形式: | CHIP CARRIER, HEAT SINK/SLUG, VERY THIN PROFILE | 峰值回流温度(摄氏度): | 260 |

| 传播延迟(tpd): | 10.5 ns | 认证状态: | Not Qualified |

| 座面最大高度: | 1 mm | 最大供电电压 (Vsup): | 3.6 V |

| 最小供电电压 (Vsup): | 1.2 V | 标称供电电压 (Vsup): | 2.7 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | AUTOMOTIVE | 端子面层: | Nickel/Palladium/Gold (Ni/Pd/Au) |

| 端子形式: | NO LEAD | 端子节距: | 0.5 mm |

| 端子位置: | QUAD | 处于峰值回流温度下的最长时间: | 30 |

| 宽度: | 2.5 mm | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74LVC373ABQ-Q100 | NEXPERIA |

获取价格 |

Octal D-type transparent latch with 5 V tolerant |

|

| 74LVC373AD | NXP |

获取价格 |

Octal D-type transparent latch with 5-volt tolerant inputs/outputs 3-State |

|

| 74LVC373AD | NEXPERIA |

获取价格 |

Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-stateProduction |

|

| 74LVC373AD,112 | NXP |

获取价格 |

74LVC373A - Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-State SOP 2 |

|

| 74LVC373AD,118 | NXP |

获取价格 |

74LVC373A - Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-State SOP 2 |

|

| 74LVC373ADB | NXP |

获取价格 |

Octal D-type transparent latch with 5-volt tolerant inputs/outputs 3-State |

|

| 74LVC373ADB,112 | NXP |

获取价格 |

74LVC373A - Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-State SSOP2 |

|

| 74LVC373ADB,118 | NXP |

获取价格 |

74LVC373A - Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-State SSOP2 |

|

| 74LVC373ADB-Q100 | NEXPERIA |

获取价格 |

Octal D-type transparent latch with 5 V tolerant |

|

| 74LVC373ADB-T | ETC |

获取价格 |

8-Bit D-Type Latch |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

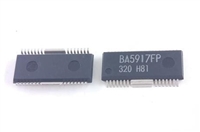

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐