| 是否Rohs认证: | 符合 | 生命周期: | Obsolete |

| 零件包装代码: | SOIC | 包装说明: | 0.300 INCH, LEAD FREE, MS-013, SOIC-20 |

| 针数: | 20 | Reach Compliance Code: | not_compliant |

| ECCN代码: | EAR99 | HTS代码: | 8542.39.00.01 |

| 风险等级: | 5.61 | 其他特性: | LOW CAPACITANCE, CMOS COMPATIBLE |

| 接口集成电路类型: | DIODE BUS TERMINATION ARRAY | JESD-30 代码: | R-PDSO-G20 |

| JESD-609代码: | e3 | 长度: | 12.8015 mm |

| 湿度敏感等级: | 1 | 功能数量: | 1 |

| 信号线数量: | 18 | 端子数量: | 20 |

| 最高工作温度: | 70 °C | 最低工作温度: | |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | SOP |

| 封装形状: | RECTANGULAR | 封装形式: | SMALL OUTLINE |

| 峰值回流温度(摄氏度): | 260 | 认证状态: | Not Qualified |

| 座面最大高度: | 2.642 mm | 表面贴装: | YES |

| 温度等级: | COMMERCIAL | 端子面层: | Matte Tin (Sn) |

| 端子形式: | GULL WING | 端子节距: | 1.27 mm |

| 端子位置: | DUAL | 处于峰值回流温度下的最长时间: | NOT SPECIFIED |

| 宽度: | 7.493 mm | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74F1071SC | FAIRCHILD |

获取价格 |

18-Bit Undershoot/Overshoot Clamp |

|

| 74F1071SCX | ETC |

获取价格 |

COMMON ANODE DIODE ARRAY|SO |

|

| 74F1071SCX_NL | FAIRCHILD |

获取价格 |

18-Bit Undershoot/Overshoot Clamp and ESD Protection Device |

|

| 74F109 | FAIRCHILD |

获取价格 |

Dual JK Positive Edge-Triggered Flip-Flop |

|

| 74F109 | NXP |

获取价格 |

Positive J-K positive edge-triggered flip-flops |

|

| 74F109_00 | FAIRCHILD |

获取价格 |

Dual JK Positive Edge-Triggered Flip-Flop |

|

| 74F109D | YAGEO |

获取价格 |

J-Kbar Flip-Flop, F/FAST Series, 2-Func, Positive Edge Triggered, 2-Bit, Complementary Out |

|

| 74F109DC | ETC |

获取价格 |

J-K-Type Flip-Flop |

|

| 74F109DCQM | FAIRCHILD |

获取价格 |

J-K Flip-Flop, 2-Func, Positive Edge Triggered, TTL, CDIP16, |

|

| 74F109DCQR | FAIRCHILD |

获取价格 |

J-Kbar Flip-Flop, F/FAST Series, 2-Func, Positive Edge Triggered, 2-Bit, Complementary Out |

|

晶闸管的静态特性与伏安特性详解

晶闸管的静态特性与伏安特性详解

贴片电容的工作原理与参数识别

贴片电容的工作原理与参数识别

精密电路设计中的高精电阻:分流电阻

精密电路设计中的高精电阻:分流电阻

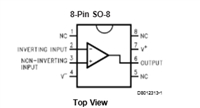

LM7131ACM5手册详解:微型高速单电源运算放大器的深度剖析

LM7131ACM5手册详解:微型高速单电源运算放大器的深度剖析