| 是否Rohs认证: | 符合 | 生命周期: | Obsolete |

| 零件包装代码: | SOIC | 包装说明: | SOP, SOP16,.25 |

| 针数: | 16 | Reach Compliance Code: | compliant |

| HTS代码: | 8542.39.00.01 | 风险等级: | 5.11 |

| 系列: | F/FAST | JESD-30 代码: | R-PDSO-G16 |

| JESD-609代码: | e3 | 长度: | 9.9 mm |

| 逻辑集成电路类型: | J-KBAR FLIP-FLOP | 最大频率@ Nom-Sup: | 90000000 Hz |

| 最大I(ol): | 0.02 A | 湿度敏感等级: | 1 |

| 位数: | 2 | 功能数量: | 2 |

| 端子数量: | 16 | 最高工作温度: | 70 °C |

| 最低工作温度: | 输出极性: | COMPLEMENTARY | |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | SOP |

| 封装等效代码: | SOP16,.25 | 封装形状: | RECTANGULAR |

| 封装形式: | SMALL OUTLINE | 包装方法: | TAPE AND REEL |

| 峰值回流温度(摄氏度): | 260 | 电源: | 5 V |

| 最大电源电流(ICC): | 17 mA | 传播延迟(tpd): | 9.2 ns |

| 认证状态: | Not Qualified | 座面最大高度: | 1.75 mm |

| 子类别: | FF/Latches | 最大供电电压 (Vsup): | 5.5 V |

| 最小供电电压 (Vsup): | 4.5 V | 标称供电电压 (Vsup): | 5 V |

| 表面贴装: | YES | 技术: | TTL |

| 温度等级: | COMMERCIAL | 端子面层: | Matte Tin (Sn) |

| 端子形式: | GULL WING | 端子节距: | 1.27 mm |

| 端子位置: | DUAL | 处于峰值回流温度下的最长时间: | NOT SPECIFIED |

| 触发器类型: | POSITIVE EDGE | 宽度: | 3.9 mm |

| 最小 fmax: | 90 MHz | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74F109SC_NL | FAIRCHILD |

获取价格 |

J-Kbar Flip-Flop, F/FAST Series, 2-Func, Positive Edge Triggered, 2-Bit, Complementary Out |

|

| 74F109SJ | FAIRCHILD |

获取价格 |

Dual JK Positive Edge-Triggered Flip-Flop |

|

| 74F109SJ | NSC |

获取价格 |

Dual JK Positive Edge-Triggered Flip-Flop |

|

| 74F109SJ | TI |

获取价格 |

Dual JK (Note: Overbar Over the K) Positive Edge-Triggered Flip-Flop |

|

| 74F109SJX | TI |

获取价格 |

F/FAST SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO16 |

|

| 74F109SJX | ONSEMI |

获取价格 |

IC FF JK TYPE DUAL 1BIT 16SOP |

|

| 74F109_00 | FAIRCHILD |

获取价格 |

Dual JK Positive Edge-Triggered Flip-Flop |

|

| 74F10D | YAGEO |

获取价格 |

NAND Gate, F/FAST Series, 3-Func, 3-Input, TTL, PDSO14 |

|

| 74F10D-T | YAGEO |

获取价格 |

NAND Gate, F/FAST Series, 3-Func, 3-Input, TTL, PDSO14 |

|

| 74F10DC | FAIRCHILD |

获取价格 |

NAND Gate, F/FAST Series, 3-Func, 3-Input, TTL, CDIP14, CERAMIC, DIP-14 |

|

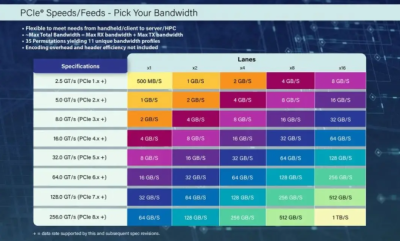

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

闪迪预警:NAND闪存供应短缺将持续至2026年

闪迪预警:NAND闪存供应短缺将持续至2026年