| 是否无铅: | 不含铅 | 生命周期: | Obsolete |

| 包装说明: | SOIC-20 | Reach Compliance Code: | unknown |

| Factory Lead Time: | 1 week | 风险等级: | 5.64 |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74LVTH573WMX | FAIRCHILD |

获取价格 |

Low Voltage Octal Transparent Latch with 3-STATE Outputs |

|

| 74LVTH573WMX | ROCHESTER |

获取价格 |

LVT SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20, 0.300 INCH, MS-013, SOIC-20 |

|

| 74LVTH573WMX | ONSEMI |

获取价格 |

IC LATCH TRANSP OCT 3ST 20SOIC |

|

| 74LVTH573_08 | FAIRCHILD |

获取价格 |

74LVT573, 74LVTH573 Low Voltage Octal Transparent Latch with 3-STATE Outputs |

|

| 74LVTH574 | FAIRCHILD |

获取价格 |

Low Voltage Octal D-Type Flip-Flop with 3-STATE Outputs |

|

| 74LVTH574 | NXP |

获取价格 |

3.3 V octal D-type flip-flop; 3-state |

|

| 74LVTH574D | NXP |

获取价格 |

3.3 V octal D-type flip-flop; 3-state |

|

| 74LVTH574D,112 | NXP |

获取价格 |

74LVT(H)574 - 3.3 V octal D-type flip-flop; 3-state SOP 20-Pin |

|

| 74LVTH574D,118 | NXP |

获取价格 |

74LVT(H)574 - 3.3 V octal D-type flip-flop; 3-state SOP 20-Pin |

|

| 74LVTH574DB | NXP |

获取价格 |

3.3 V octal D-type flip-flop; 3-state |

|

国产x86处理器里程碑!兆芯6000台医疗电脑中标某总医院

国产x86处理器里程碑!兆芯6000台医疗电脑中标某总医院

稚晖君团队开源GO-1模型:ViLLA架构如何重塑具身智能未来?

稚晖君团队开源GO-1模型:ViLLA架构如何重塑具身智能未来?

安森美收购奥拉半导体Vcore技术 抢占AI数据中心电源管理制高点

安森美收购奥拉半导体Vcore技术 抢占AI数据中心电源管理制高点

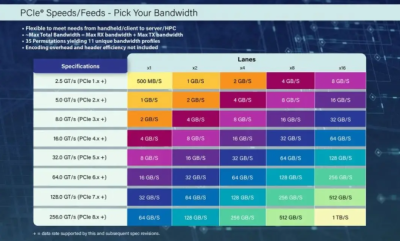

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代