| 生命周期: | Active | 零件包装代码: | TSSOP2 |

| 包装说明: | TSSOP, | 针数: | 20 |

| Reach Compliance Code: | compliant | 风险等级: | 5.79 |

| 其他特性: | ALSO OPERATES AT 1.65 TO 3.6V SUPPLY | 系列: | LVC/LCX/Z |

| JESD-30 代码: | R-PDSO-G20 | 长度: | 6.5 mm |

| 逻辑集成电路类型: | BUS DRIVER | 位数: | 8 |

| 功能数量: | 1 | 端口数量: | 2 |

| 端子数量: | 20 | 最高工作温度: | 125 °C |

| 最低工作温度: | -40 °C | 输出特性: | 3-STATE |

| 输出极性: | TRUE | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | TSSOP | 封装形状: | RECTANGULAR |

| 封装形式: | SMALL OUTLINE, THIN PROFILE, SHRINK PITCH | 峰值回流温度(摄氏度): | NOT SPECIFIED |

| 传播延迟(tpd): | 18.8 ns | 筛选级别: | AEC-Q100 |

| 座面最大高度: | 1.1 mm | 最大供电电压 (Vsup): | 3.6 V |

| 最小供电电压 (Vsup): | 1.2 V | 标称供电电压 (Vsup): | 3.3 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | AUTOMOTIVE | 端子形式: | GULL WING |

| 端子节距: | 0.65 mm | 端子位置: | DUAL |

| 处于峰值回流温度下的最长时间: | NOT SPECIFIED | 宽度: | 4.4 mm |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74LVC374APW-Q100J | NXP |

获取价格 |

74LVC374A-Q100 - Octal D-type flip-flop; 5 V tolerance; positive edge-trigger; 3-state TSS |

|

| 74LVC374APW-T | ETC |

获取价格 |

Octal D-Type Flip-Flop |

|

| 74LVC374APY | IDT |

获取价格 |

SSOP-20, Tube |

|

| 74LVC374A-Q100 | NEXPERIA |

获取价格 |

Octal D-type flip-flop with 5 V tolerant inputs/outputs; positive edge-trigger; 3-state |

|

| 74LVC374AQ8 | IDT |

获取价格 |

QSOP-20, Reel |

|

| 74LVC374ASO | IDT |

获取价格 |

SOIC-20, Tube |

|

| 74LVC374ATTR | STMICROELECTRONICS |

获取价格 |

OCTAL D-TYPE FLIP-FLOP HIGH PERFORMANCE |

|

| 74LVC374PW | PHILIPS |

获取价格 |

D Flip-Flop, 8-Func, Positive Edge Triggered, CMOS, PDSO20 |

|

| 74LVC374PW | NXP |

获取价格 |

LVC/LCX/Z SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

|

| 74LVC374PWDH | NXP |

获取价格 |

LVC/LCX/Z SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

|

SZNUP2105LT1G电气参数、产品特性详解

SZNUP2105LT1G电气参数、产品特性详解

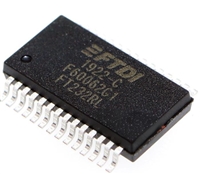

FT232RL资料解读:引脚说明、参数详情、产品特性

FT232RL资料解读:引脚说明、参数详情、产品特性

RC0402FR-07100KL资料解读:电气参数、产品特性

RC0402FR-07100KL资料解读:电气参数、产品特性

RC0603FR-070R数据手册解读:特性、应用与替换型号推荐

RC0603FR-070R数据手册解读:特性、应用与替换型号推荐