ISL6615A

Description

PWM

1.18V < PWM < 2.36V

0.76V < PWM < 1.96V

t

t

PDLU

PDHU

t

TSSHD

t

PDTS

t

PDTS

t

FU

UGATE

LGATE

t

RU

t

t

FL

RL

t

t

TSSHD

PDLL

t

PDHL

FIGURE 1. TIMING DIAGRAM

lower MOSFETs from conducting simultaneously. This is

accomplished by ensuring the rising gate turns on its MOSFET

with minimum and sufficient delay after the other has turned off.

Operation

Designed for versatility and speed, the ISL6615A MOSFET driver

controls both high-side and low-side N-Channel FETs of a half-

bridge power train from one externally provided PWM signal.

During turn-off of the lower MOSFET, the LGATE voltage is

monitored until it drops below 1.75V. Prior to reaching this level,

there is a 25ns blanking period to protect against sudden dips in

the LGATE voltage. Once 1.75V is reached, the UGATE is released

to rise after 20ns of propagation delay. Once the PHASE is high,

the adaptive shoot-through circuitry monitors the PHASE and

UGATE voltages during PWM falling edge and subsequent UGATE

turn-off. If PHASE falls to less than +0.8V, the LGATE is released

to turn on after 10ns of propagation delay. If the UGATE-PHASE

falls to less than 1.75V and after 40ns of propagation delay,

LGATE is released to rise.

Prior to VCC exceeding its POR level, the Pre-POR overvoltage

protection function is activated during initial start-up; the upper

gate (UGATE) is held low and the lower gate (LGATE), controlled

by the Pre-POR overvoltage protection circuits, is connected to

the PHASE. Once the VCC voltage surpasses the VCC Rising

Threshold (see “Electrical Specifications” on page 4) the PWM

signal takes control of gate transitions. A rising edge on PWM

initiates the turn-off of the lower MOSFET (see “TIMING

DIAGRAM” on page 6). After a short propagation delay [t

the lower gate begins to fall. Typical fall times [t ] are provided

],

PDLL

FL

in the “Electrical Specifications” on page 4. Adaptive shoot-

through circuitry monitors the LGATE voltage and determines the

Tri-state PWM Input

A unique feature of these drivers and other Intersil drivers is the

addition of a shutdown window to the PWM input. If the PWM

signal enters and remains within the shutdown window for a set

holdoff time, the driver outputs are disabled and both MOSFET

gates are pulled and held low. The shutdown state is removed

when the PWM signal moves outside the shutdown window.

Otherwise, the PWM rising and falling thresholds outlined in

“Electrical Specifications” on page 4, determine when the lower

and upper gates are enabled.

upper gate delay time [t

]. This prevents both the lower and

upper MOSFETs from conducting simultaneously. Once this delay

PDHU

period is complete, the upper gate drive begins to rise [t ] and

RU

the upper MOSFET turns on.

A falling transition on PWM results in the turn-off of the upper

MOSFET and the turn-on of the lower MOSFET. A short

propagation delay [t

] is encountered before the upper gate

PDLU

begins to fall [t ]. Again, the adaptive shoot-through circuitry

FU

determines the lower gate delay time, t

. The PHASE voltage

PDHL

This feature helps prevent a negative transient on the output

voltage when the output is shut down, eliminating the Schottky

diode that is used in some systems for protecting the load from

reversed output voltage events.

and the UGATE voltage are monitored, and the lower gate is

allowed to rise after PHASE drops below a level or the voltage of

UGATE to PHASE reaches a level depending upon the current

direction (See the following section titled “Advanced Adaptive

Zero Shoot-Through Dead-Time Control” for details). The lower

In addition, more than 400mV hysteresis also incorporates into

the Tri-State shutdown window to eliminate PWM input

oscillations due to the capacitive load seen by the PWM input

through the body diode of the controller’s PWM output when the

power-up and/or power-down sequence of bias supplies of the

driver and PWM controller are required.

gate then rises [t ], turning on the lower MOSFET.

RL

Advanced Adaptive Zero Shoot-Through

Dead-time Control

The ISL6615A driver incorporates a unique adaptive dead-time

control technique to minimize dead-time, resulting in high

efficiency from the reduced freewheeling time of the lower

MOSFETs’ body-diode conduction, and to prevent the upper and

FN6608 Rev 2.00

April 13, 2012

Page 6 of 13

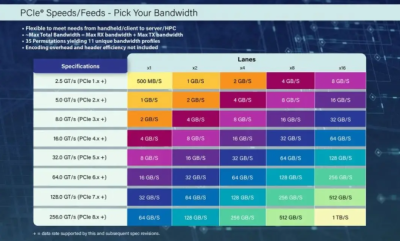

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

闪迪预警:NAND闪存供应短缺将持续至2026年

闪迪预警:NAND闪存供应短缺将持续至2026年