| 生命周期: | Obsolete | 包装说明: | , |

| Reach Compliance Code: | unknown | 风险等级: | 5.84 |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| ICS8701ICYIT | IDT |

获取价格 |

Clock Driver |

|

| ICS8702 | ICSI |

获取价格 |

LOW SKEW ±1, ±2 CLOCK GENERATOR |

|

| ICS87021AMIT | IDT |

获取价格 |

Low Skew Clock Driver, 87021 Series, 2 True Output(s), 0 Inverted Output(s), PDSO8, 3.90 X |

|

| ICS8702BY | ICSI |

获取价格 |

LOW SKEW ±1, ±2 CLOCK GENERATOR |

|

| ICS8702BYLF | IDT |

获取价格 |

Low Skew Clock Driver, 8702 Series, 20 True Output(s), 0 Inverted Output(s), PQFP48, 7 X 7 |

|

| ICS8702BYLFT | IDT |

获取价格 |

Low Skew Clock Driver, 8702 Series, 20 True Output(s), 0 Inverted Output(s), PQFP48, 7 X 7 |

|

| ICS8702BYT | ICSI |

获取价格 |

LOW SKEW ±1, ±2 CLOCK GENERATOR |

|

| ICS8702BY-T | IDT |

获取价格 |

Clock Driver, 8702 Series, 20 True Output(s), 0 Inverted Output(s), PQFP48, 7 X 7 MM, 1.40 |

|

| ICS8705 | IDT |

获取价格 |

ZERO DELAY, DIFFERENTIAL-TO-LVCMOS/LVTTL CLOCK GENERATOR |

|

| ICS8705 | ICSI |

获取价格 |

ZERO DELAY, DIFFERENTIAL-TO-LVCMOS/LVTTL CLOCK GENERATOR |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

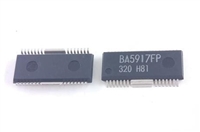

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐