| 是否Rohs认证: | 符合 | 生命周期: | Active |

| Reach Compliance Code: | unknown | 风险等级: | 5.8 |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| DS31404 | MAXIM |

获取价格 |

4-Input, 8-Output, Dual DPLL Timing IC with Sub-ps Output Jitter Differential |

|

| DS31404 | MICROCHIP |

获取价格 |

The DS31400 is a flexible, high-performance timing IC for diverse frequency conversion and |

|

| DS31404GN+ | MAXIM |

获取价格 |

4-Input, 8-Output, Dual DPLL Timing IC with Sub-ps Output Jitter Differential |

|

| DS31406 | MAXIM |

获取价格 |

2-Input, 14-Output, Single DPLL Timing IC with Sub-ps Output Jitter |

|

| DS31406 | MICROCHIP |

获取价格 |

The DS31406 is a flexible, high-performance timing IC for diverse frequency conversion and |

|

| DS31406GN+ | MAXIM |

获取价格 |

2-Input, 14-Output, Single DPLL Timing IC with Sub-ps Output Jitter |

|

| DS31407 | MAXIM |

获取价格 |

3-Input, 4-Output, Single DPLL Timing IC with Sub-ps Output Jitter Differential |

|

| DS31407 | MICROCHIP |

获取价格 |

The DS31407 is a flexible, high-performance timing IC for diverse frequency conversion and |

|

| DS31407GN+ | MAXIM |

获取价格 |

3-Input, 4-Output, Single DPLL Timing IC with Sub-ps Output Jitter Differential |

|

| DS31408 | MAXIM |

获取价格 |

8-Input, 14-Output, Dual DPLL Timing IC with Sub-ps Output Jitter and 1588 Clock |

|

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

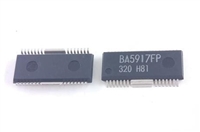

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐