| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CY14B101P_13 | CYPRESS |

获取价格 |

1-Mbit (128 K x 8) Serial SPI nvSRAM with Real Time Clock |

|

| CY14B101PA | CYPRESS |

获取价格 |

1-Mbit (128 K × 8) Serial (SPI) nvSRAM with R |

|

| CY14B101PA_1107 | CYPRESS |

获取价格 |

1-Mbit (128 K x 8) Automotive Serial (SPI) nvSRAM with Real Time Clock |

|

| CY14B101PA_12 | CYPRESS |

获取价格 |

1-Mbit (128 K Ã 8) Serial (SPI) nvSRAM with |

|

| CY14B101PA-SF104XI | CYPRESS |

获取价格 |

1-Mbit (128 K × 8) Serial (SPI) nvSRAM with R |

|

| CY14B101PA-SF104XIT | CYPRESS |

获取价格 |

1-Mbit (128 K × 8) Serial (SPI) nvSRAM with R |

|

| CY14B101PA-SFXI | CYPRESS |

获取价格 |

1-Mbit (128 K × 8) Serial (SPI) nvSRAM with R |

|

| CY14B101PA-SFXI | INFINEON |

获取价格 |

nvSRAM (non-volatile SRAM) |

|

| CY14B101PA-SFXIT | CYPRESS |

获取价格 |

1-Mbit (128 K × 8) Serial (SPI) nvSRAM with R |

|

| CY14B101PA-SFXIT | INFINEON |

获取价格 |

nvSRAM (non-volatile SRAM) |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

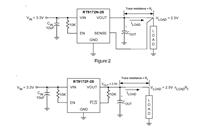

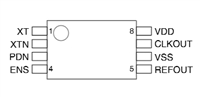

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征