| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| AS7C1024B-20TJC | ALSC |

获取价格 |

5V 128K X 8 CMOS SRAM |

|

| AS7C1024B-20TJCN | ALSC |

获取价格 |

5V 128K X 8 CMOS SRAM |

|

| AS7C1024B-20TJI | ALSC |

获取价格 |

5V 128K X 8 CMOS SRAM |

|

| AS7C1024B-20TJIN | ALSC |

获取价格 |

5V 128K X 8 CMOS SRAM |

|

| AS7C1024C | ALSC |

获取价格 |

5V 128K X 8 CMOS SRAM |

|

| AS7C1024L-10JC | ETC |

获取价格 |

x8 SRAM |

|

| AS7C1024L-10PC | ALSC |

获取价格 |

Standard SRAM, 128KX8, 10ns, CMOS, PDIP32 |

|

| AS7C1024L-10TC | ALSC |

获取价格 |

Standard SRAM, 128KX8, 10ns, CMOS, PDSO32 |

|

| AS7C1024L-10TPC | ETC |

获取价格 |

x8 SRAM |

|

| AS7C1024L-12JC | ETC |

获取价格 |

x8 SRAM |

|

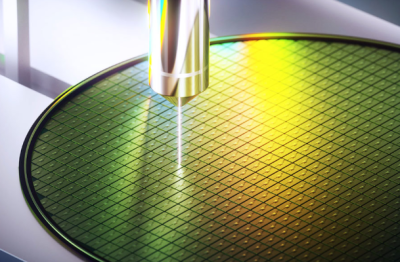

日本芯片代工厂JS Foundry濒临破产 激进扩张致负债161亿日元

日本芯片代工厂JS Foundry濒临破产 激进扩张致负债161亿日元

LG电子进军HBM制造关键领域 混合键合设备研发瞄准2028年量产

LG电子进军HBM制造关键领域 混合键合设备研发瞄准2028年量产

博通10亿美元半导体工厂计划搁浅 西班牙谈判破裂背后暗藏政治变局

博通10亿美元半导体工厂计划搁浅 西班牙谈判破裂背后暗藏政治变局

英特尔联手台积电2nm工艺 Nova Lake芯片流片完成引爆业界期待

英特尔联手台积电2nm工艺 Nova Lake芯片流片完成引爆业界期待