| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| K4B4G1646E | SAMSUNG |

获取价格 |

4Gb E-die DDR3L SDRAM |

|

| K4B4G1646E-BMK0 | SAMSUNG |

获取价格 |

4Gb E-die DDR3L SDRAM |

|

| K4B4G1646E-BMMA | SAMSUNG |

获取价格 |

4Gb E-die DDR3L SDRAM |

|

| K4B4G1646E-BYK0 | SAMSUNG |

获取价格 |

4Gb E-die DDR3L SDRAM |

|

| K4B4G1646E-BYMA | SAMSUNG |

获取价格 |

4Gb E-die DDR3L SDRAM |

|

| K4B4G1646Q | SAMSUNG |

获取价格 |

4Gb Q-die DDR3L SDRAM Olny x16 96FBGA with Lead-Free & Halogen-Free (RoHS compliant) 1.35V |

|

| K4B4G1646Q-HYF8 | SAMSUNG |

获取价格 |

4Gb Q-die DDR3L SDRAM Olny x16 96FBGA with Lead-Free & Halogen-Free (RoHS compliant) 1.35V |

|

| K4B4G1646Q-HYH9 | SAMSUNG |

获取价格 |

4Gb Q-die DDR3L SDRAM Olny x16 96FBGA with Lead-Free & Halogen-Free (RoHS compliant) 1.35V |

|

| K4B4G1646Q-HYK0 | SAMSUNG |

获取价格 |

4Gb Q-die DDR3L SDRAM Olny x16 96FBGA with Lead-Free & Halogen-Free (RoHS compliant) 1.35V |

|

| K4C560838C-TCA | SAMSUNG |

获取价格 |

Synchronous DRAM, 32MX8, 0.85ns, CMOS, PDSO66, 0.400 X 0.875 INCH, 0.65 MM PITCH, PLASTIC, |

|

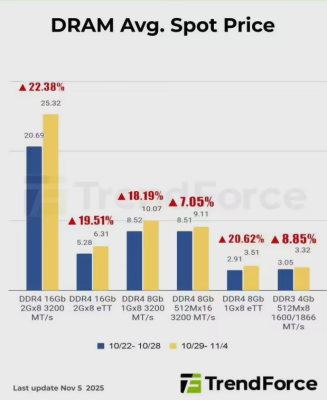

内存市场惊现抢购潮!DDR5芯片一周暴涨30%背后暗藏什么玄机?

内存市场惊现抢购潮!DDR5芯片一周暴涨30%背后暗藏什么玄机?

京东1号车震撼下线:10万内超500km续航国民车来了

京东1号车震撼下线:10万内超500km续航国民车来了

华邦电预警:内存结构性缺货将持续至2027年,AI需求引爆存储涨价潮

华邦电预警:内存结构性缺货将持续至2027年,AI需求引爆存储涨价潮

英伟达联手德国电信豪掷10亿欧元 打造欧洲AI算力新标杆

英伟达联手德国电信豪掷10亿欧元 打造欧洲AI算力新标杆