| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| DSP56301VL80 | FREESCALE |

获取价格 |

24-Bit Digital Signal Processor |

|

| DSP56302 | MOTOROLA |

获取价格 |

DSP56301 Digital Signal Processor |

|

| DSP56302EMUM | ETC |

获取价格 |

DSP56302EMUM Users Manual |

|

| DSP56302UM | ETC |

获取价格 |

DSP56302 User's Manual |

|

| DSP56303 | MOTOROLA |

获取价格 |

DSP56301 Digital Signal Processor |

|

| DSP56303 | FREESCALE |

获取价格 |

DSP56303 USER’S MANUAL |

|

| DSP56303_1 | FREESCALE |

获取价格 |

24-Bit Digital Signal Processor |

|

| DSP56303AG100 | FREESCALE |

获取价格 |

24-Bit Digital Signal Processor |

|

| DSP56303EVMCL | ETC |

获取价格 |

DSP56303EVM DSP56303EVM Kit Contents List |

|

| DSP56303EVMUM | ETC |

获取价格 |

DSP56303 EVM Users Manual |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

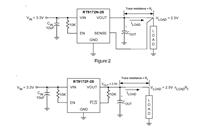

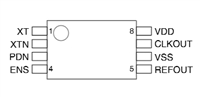

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征