| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| DS92LV040ATLQAX/NOPB | NSC |

获取价格 |

IC QUAD LINE TRANSCEIVER, PQCC44, PLASTIC, LLP-44, Line Driver or Receiver |

|

| DS92LV040ATLQAX/NOPB | TI |

获取价格 |

4 通道总线 LVDS 收发器 | NJN | 44 | -40 to 85 |

|

| DS92LV0411 | NSC |

获取价格 |

5 - 50 MHz Channel Link II Serializer/Deserializer with LVDS Parallel Interface |

|

| DS92LV0411 | TI |

获取价格 |

具有 LVDS 并行接口的 5 - 50MHz Channel Link II 串行器 |

|

| DS92LV0411SQ | NSC |

获取价格 |

5 - 50 MHz Channel Link II Serializer/Deserializer with LVDS Parallel Interface |

|

| DS92LV0411SQ/NOPB | TI |

获取价格 |

具有 LVDS 并行接口的 5 - 50MHz Channel Link II 串行器 | |

|

| DS92LV0411SQE | NSC |

获取价格 |

5 - 50 MHz Channel Link II Serializer/Deserializer with LVDS Parallel Interface |

|

| DS92LV0411SQE/NOPB | TI |

获取价格 |

具有 LVDS 并行接口的 5 - 50MHz Channel Link II 串行器 | |

|

| DS92LV0411SQENOPB | NSC |

获取价格 |

IC LINE DRIVER, QCC36, 6 X 6 MM, 0.80 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, LLP-36, Li |

|

| DS92LV0411SQNOPB | NSC |

获取价格 |

IC LINE DRIVER, QCC36, 6 X 6 MM, 0.80 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, LLP-36, Li |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

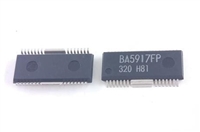

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐