| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CY7C4281-10JIT | CYPRESS |

获取价格 |

FIFO, 64KX9, 8ns, Synchronous, CMOS, PQCC32, PLASTIC, LCC-32 |

|

| CY7C4281-15JC | CYPRESS |

获取价格 |

64K/128K x 9 Deep Sync FIFOs |

|

| CY7C4281-25JC | CYPRESS |

获取价格 |

64K/128K x 9 Deep Sync FIFOs |

|

| CY7C4281-25JCR | CYPRESS |

获取价格 |

暂无描述 |

|

| CY7C4281-25JI | CYPRESS |

获取价格 |

FIFO, 64KX9, 15ns, Synchronous, CMOS, PQCC32, PLASTIC, LCC-32 |

|

| CY7C4281V | CYPRESS |

获取价格 |

16K/32K/64K/128K x 9 Low-Voltage Deep Sync FIFOs |

|

| CY7C4281V-10JC | CYPRESS |

获取价格 |

16K/32K/64K/128K x 9 Low-Voltage Deep Sync FIFOs |

|

| CY7C4281V-10JXC | CYPRESS |

获取价格 |

16K/32K/64K/128K x 9 Low-Voltage Deep Sync⑩ F |

|

| CY7C4281V-15JC | CYPRESS |

获取价格 |

16K/32K/64K/128K x 9 Low-Voltage Deep Sync FIFOs |

|

| CY7C4281V-15JCR | CYPRESS |

获取价格 |

FIFO, 64KX9, Synchronous, CMOS, PQCC32, PLASTIC, LCC-32 |

|

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

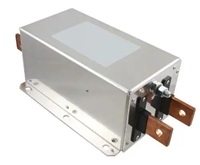

网络滤波器、EMI滤波器与EMC滤波器在电子元器件中的分类关系

网络滤波器、EMI滤波器与EMC滤波器在电子元器件中的分类关系

NTC热敏电阻与PTC热敏电阻的应用原理及选型原则

NTC热敏电阻与PTC热敏电阻的应用原理及选型原则