| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CY54FCT543TDMB | TI |

获取价格 |

8-Bit Latched Registered Transceiver |

|

| CY54FCT543TLM | ETC |

获取价格 |

Single 8-bit Bus Transceiver |

|

| CY54FCT543TLMB | TI |

获取价格 |

8-BIT LATCHED REGISTERED TRANSCEIVERS WITH 3-STATE OUTPUTS |

|

| CY54FCT543TLMB | CYPRESS |

获取价格 |

Registered Bus Transceiver, FCT Series, 1-Func, 8-Bit, True Output, CMOS, CQCC28, CERAMIC, |

|

| CY54FCT543TQSOP | TI |

获取价格 |

8-Bit Latched Registered Transceiver |

|

| CY54FCT543TSOIC | TI |

获取价格 |

8-Bit Latched Registered Transceiver |

|

| CY54FCT573ATDM | CYPRESS |

获取价格 |

Bus Driver, FCT Series, 1-Func, 8-Bit, True Output, CMOS, CDIP20, 0.300 INCH, CERDIP-20 |

|

| CY54FCT573ATLM | CYPRESS |

获取价格 |

Bus Driver, FCT Series, 1-Func, 8-Bit, True Output, CMOS, CQCC20, LCC-20 |

|

| CY54FCT573ATLMB | TI |

获取价格 |

8-BIT LATCHES WITH 3-STATE OUTPUTS |

|

| CY54FCT573CTDM | CYPRESS |

获取价格 |

Bus Driver, FCT Series, 1-Func, 8-Bit, True Output, CMOS, CDIP20, 0.300 INCH, CERDIP-20 |

|

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

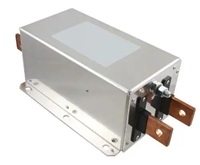

网络滤波器、EMI滤波器与EMC滤波器在电子元器件中的分类关系

网络滤波器、EMI滤波器与EMC滤波器在电子元器件中的分类关系

NTC热敏电阻与PTC热敏电阻的应用原理及选型原则

NTC热敏电阻与PTC热敏电阻的应用原理及选型原则