SPI Interface, Quad SPST Switch, Low QINJ,

Low CON, 15 V/+12 V, Mux Configurable

ADGS1212

Data Sheet

FEATURES

FUNCTIONAL BLOCK DIAGRAM

SPI interface with error detection

Includes CRC, invalid read/write address, and SCLK count

error detection

ADGS1212

S1

S2

S3

S4

D1

D2

D3

D4

Supports burst mode and daisy-chain mode

Industry-standard SPI Mode 0 and SPI Mode 3 compatible

Guaranteed break-before-make switching allowing external

wiring of switches to deliver multiplexer configurations

VSS to VDD analog signal range

Fully specified at 1ꢀ V and +12 V supply

4.ꢀ V to 16.ꢀ V dual-supply operation

ꢀ V to 16.ꢀ V single-supply operation

SPI

INTERFACE

SDO

Ultralow capacitance and leakage allows fast settling time

1 pF typical off switch drain capacitance at 2ꢀ°C, 1ꢀ V

2.6 pF typical on switch capacitance at 2ꢀ°C, 1ꢀ V

<1 pC typical charge injection at 2ꢀ°C

SCLK SDI CS RESET/V

L

Figure 1.

1.8 V logic compatibility with 2.7 V ≤ VL ≤ 3.3 V

APPLICATIONS

In the off condition, signal levels up to the supplies are blocked.

Automated test equipment

Data acquisition systems

Battery-powered systems

Sample-and-hold systems

Audio signal routing

The ultralow capacitance and charge injection of these switches

make them ideal solutions for data acquisition and sample-and-

hold applications where low glitch and fast settling are required.

Fast switching speed coupled with high signal bandwidth make

the device suitable for video signal switching.

Video signal routing

Communications systems

Multifunction pin names may be referenced by their relevant

function only.

GENERAL DESCRIPTION

PRODUCT HIGHLIGHTS

The ADGS1212 contains four independent single-pole/single-

throw (SPST) switches. A serial peripheral interface (SPI)

controls the switches. The SPI interface has robust error detection

features such as cyclic redundancy check (CRC) error detection,

invalid read/write address detection, and SCLK count error

detection.

1. SPI interface removes the need for parallel conversion,

logic traces, and reduces the general-purpose input/output

(GPIO) channel count.

2. Daisy-chain mode removes additional logic traces when

multiple devices are used.

3. CRC error detection, invalid read/write address detection,

and SCLK count error detection ensure a robust digital

interface.

4. CRC and error detection capabilities allow the ADGS1212

to be used in safety critical systems.

5. Guaranteed break-before-make switching allows the the

ADGS1212 to be used in multiplexer configurations with

external wiring.

6. The ADGS1212 1.8 V logic compatibility with 2.7 V ≤ VL ≤

3.3 V

It is possible to daisy-chain multiple ADGS1212 devices together.

Daisy-chain mode enables the configuration of multiple devices

with minimal digital lines. The ADGS1212 can also operate in

burst mode to decrease the time between SPI commands.

iCMOS construction ensures ultralow power dissipation, making

the device ideal for portable and battery-powered instruments.

Each switch conducts equally well in both directions when on,

and each switch has an input signal range that extends to the

supplies.

7. Ultralow capacitance.

8. <1 pC charge injection.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registeredtrademarks arethe property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Technical Support

©2017 Analog Devices, Inc. All rights reserved.

www.analog.com

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

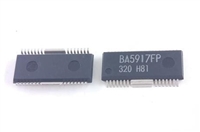

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐