SpecificatiiosnpsGispAGLA2L222VV1100

In-System Programmable E2CMOS PLD

Generic Array Logic™

FEATURES

FUNCTIONAL BLOCK DIAGRAM

• IN-SYSTEM PROGRAMMABLE™ (5-V ONLY)

— 4-Wire Serial Programming Interface

RESET

I/CLK

— Minimum 10,000 Program/Erase Cycles

— Built-in Pull-Down on SDI Pin Eliminates Discrete

Resistor on Board (ispGAL22V10C Only)

8

OLMC

I/O/Q

I

10

• HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— 7.5 ns Maximum Propagation Delay

— Fmax = 111 MHz

OLMC

I/O/Q

I

12

I

— 5 ns Maximum from Clock Input to Data Output

OLMC

I/O/Q

— UltraMOS® Advanced CMOS Technology

14

I

• ACTIVE PULL-UPS ON ALL LOGIC INPUT AND I/O PINS

OLMC

I/O/Q

• COMPATIBLE WITH STANDARD 22V10 DEVICES

— Fully Function/Fuse-Map/Parametric Compatible

with Bipolar and CMOS 22V10 Devices

I

16

OLMC

I/O/Q

I

• E2 CELL TECHNOLOGY

— In-System Programmable Logic

— 100% Tested/100% Yields

16

OLMC

I/O/Q

I

14

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

OLMC

I/O/Q

I

• TEN OUTPUT LOGIC MACROCELLS

— Maximum Flexibility for Complex Logic Designs

12

OLMC

I

I

I

I/O/Q

I/O/Q

I/O/Q

• APPLICATIONS INCLUDE:

— DMA Control

— State Machine Control

— High Speed Graphics Processing

— Software-Driven Hardware Configuration

10

OLMC

OLMC

8

SDO

SDI

MODE

SCLK

PROGRAMMING

LOGIC

• ELECTRONIC SIGNATURE FOR IDENTIFICATION

DESCRIPTION

PRESET

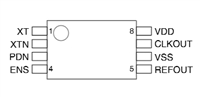

PIN CONFIGURATION

PLCC

The ispGAL22V10, at 7.5ns maximum propagation delay time,

combines a high performance CMOS process with Electrically

Erasable (E2) floating gate technology to provide the industry's

first in-system programmable 22V10 device. E2 technology of-

fers high speed (<100ms) erase times, providing the ability to re-

program or reconfigure the device quickly and efficiently.

SSOP

4

2

28

26

The generic architecture provides maximum design flexibility by

allowing the Output Logic Macrocell (OLMC) to be configured by

the user. The ispGAL22V10 is fully function/fuse map/parametric

compatible with standard bipolar and CMOS 22V10 devices. The

standard PLCC package provides the same functional pinout as

the standard 22V10 PLCC package with No-Connect pins being

used for the ISP interface signals.

1

7

28

22

Vcc

SCLK

I

I

I

5

7

2 5 I/O/Q

I/O/Q

I/CLK

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

SDO

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

I

I

I

ispGAL

22V10

2 3

I/O/Q

ispGAL22V10

Top View

I

I

MODE

SDO

MODE

I

Top View

I

I

I

I/O/Q

I/O/Q

9

21

I

I

I

I

Unique test circuitry and reprogrammable cells allow complete

AC, DC, and functional testing during manufacture. As a result,

Lattice Semiconductor delivers 100% field programmability and

functionality of all GAL products. In addition, 10,000 erase/write

cycles and data retention in excess of 20 years are specified.

11

1 9 I/O/Q

18

12

1 4

1 6

14

15

SDI

GND

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 681-0118; 1-888-ISP-PLDS; FAX (503) 681-3037; http://www.latticesemi.com

July 1997

isp22v10_02

1

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

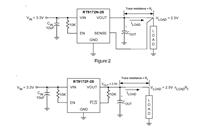

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征