Application Note 1593

Author: Jeff Lies

Add a Loss of Signal (LOS) Indicator to Your RS-485 or

RS-422 Transceiver

Rx Failsafe

In RS-485/RS-422 terminology, “failsafe” is used to indicate

Introduction

A desirable feature on any network may be a Loss of Signal

Rx functionality that drives the Rx output to a known state

(LOS) indicator. Such an indicator alerts a monitoring controller

when common bus faults occur. The logic high state typically

that a potentially serious network error has occurred, thereby

represents the idle (no transmission in progress) state, so

allowing for notification and/or intervention. In an RS-485/

driving the Rx output to a logic high under fault conditions is

RS-422 network, a LOS may occur if a connector disconnects

the usual failsafe implementation. Without the failsafe

from a board, if a cable fails, or if the network driver fails or

function, an Rx output’s inadvertant logic low, or oscillation,

loses power. When this occurs, bus activity ceases - as shown

might be interpreted as a message start bit. This could cause a

in Figure 1 - and an LOS detector would assert its output. This

processor to waste valuable time attempting to service

application note discusses the RS-485/RS-422 receiver (Rx)

operation, explains how the Rx interprets the differential bus

phantom messages.

voltages, and introduces a method for generating the desired

LOS indicator.

The most common form of failsafe is failsafe open, with

“open” referring to the condition where the Rx inputs are

floating. This can occur when a network bus is cut, or if the bus

connector separates from the networked device containing the

Rx. Most RS-485 Rx available today incorporate this function,

and it is typically accomplished via an internal pull-up resistor

on the noninverting (A) input. The pull-up is sized to ensure that

if the Rx inputs float, then the Rx input circuitry creates enough

of a positive offset so that the Rx comparator interprets the

input condition as a logic high.

5

LOS

3

1

The “Full-Failsafe” RS-485 Receiver

0

An improved differential Rx includes all the features

-1

mentioned previously, plus the addition of circuitry to ensure

V

BUS

that the Rx is failsafe if the differential input voltage (V ) is 0V

ID

-3

-5

(failsafe “shorted”). This condition may occur due to a cable

error (e.g., crimped), a connector error (shorted pins), or in

normally operating networks where multiple drivers operate

on a terminated bus (multi-point network). Multi-point

operation requires that all drivers be tri-statable, and there are

periods of time when all drivers are simultaneously tri-stated.

When this occurs, the differential termination resistor(s)

TIME (1µs/DIV)

FIGURE 1. TYPICAL LOS OPERATION

causes the bus voltage to collapse to the V =0V condition. As

mentioned before, V =0V is an undefined RS-485 level, so an

ID

Rx with only failsafe open functionality may generate

erroneous start bits.

ID

RS-485 Receiver (Rx) Basics

The RS-485/RS-422 Rx is a differential circuit (comparator)

that compares voltages at the noninverting and inverting

inputs (A and B), and outputs a corresponding logic level. Per

the Standards, if A-B (i.e., the differential input voltage) is

greater than +200mV, then the Rx outputs a logic high; if

A-B < -200mV, then the Rx outputs a logic low. Any differential

voltage between -200mV and +200mV is undefined, and the

Rx might output a logic high, a logic low, or may even oscillate.

The full-failsafe Rx solves this problem by ensuring that the

V

=0V condition is recognized as a logic high input, so the Rx

ID

output remains in the idle state. Full-failsafe functionality is

accomplished by designing the Rx so that the minimum input

high level is slightly negative (-10mV to -25mV), rather than the

+200mV used for standard RS-485 and RS-422 Rx. Note that

this new threshold definition remains RS-422 and RS-485

compliant.

February 1, 2011

AN1593.0

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas Inc. 2011. All Rights Reserved.

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

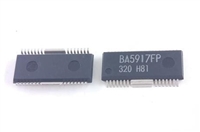

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐

2N7002DW数据手册:参数解读、引脚信息、替代型号推荐