| 是否Rohs认证: | 不符合 | 生命周期: | Obsolete |

| 零件包装代码: | TSSOP | 包装说明: | 6.10 MM, 0.50 MM PITCH, TSSOP-56 |

| 针数: | 56 | Reach Compliance Code: | compliant |

| 风险等级: | 5.92 | Is Samacsys: | N |

| JESD-30 代码: | R-PDSO-G56 | JESD-609代码: | e0 |

| 长度: | 14 mm | 湿度敏感等级: | 1 |

| 端子数量: | 56 | 最高工作温度: | 70 °C |

| 最低工作温度: | 最大输出时钟频率: | 133 MHz | |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | TSSOP |

| 封装形状: | RECTANGULAR | 封装形式: | SMALL OUTLINE, THIN PROFILE, SHRINK PITCH |

| 峰值回流温度(摄氏度): | 240 | 主时钟/晶体标称频率: | 16 MHz |

| 认证状态: | Not Qualified | 座面最大高度: | 1.2 mm |

| 最大供电电压: | 3.465 V | 最小供电电压: | 3.135 V |

| 标称供电电压: | 3.3 V | 表面贴装: | YES |

| 温度等级: | COMMERCIAL | 端子面层: | TIN LEAD |

| 端子形式: | GULL WING | 端子节距: | 0.5 mm |

| 端子位置: | DUAL | 处于峰值回流温度下的最长时间: | 20 |

| 宽度: | 6.1 mm | uPs/uCs/外围集成电路类型: | CLOCK GENERATOR, PROCESSOR SPECIFIC |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| ICS932S200G-T | IDT |

获取价格 |

Clock Generator, PDSO56 |

|

| ICS932S200YFLF-T | IDT |

获取价格 |

Processor Specific Clock Generator, 133MHz, PDSO56, 0.300 INCH, SSOP-56 |

|

| ICS932S200YF-T | ICSI |

获取价格 |

Frequency Timing Generator for Dual Server/Workstation Systems |

|

| ICS932S200YGLF-T | IDT |

获取价格 |

Processor Specific Clock Generator, 133MHz, PDSO56, 6.10 MM, 0.50 MM PITCH, TSSOP-56 |

|

| ICS932S200YG-T | ICSI |

获取价格 |

Frequency Timing Generator for Dual Server/Workstation Systems |

|

| ICS932S202 | ICSI |

获取价格 |

Frequency Timing Generator for Differential PIIIType Dual-CPU Systems |

|

| ICS932S203 | IDT |

获取价格 |

Frequency Generator with 133MHz Differential CPU Clocks |

|

| ICS932S203 | ICSI |

获取价格 |

Frequency Generator with 133MHz Differential CPU Clocks |

|

| ICS932S203AFLF | IDT |

获取价格 |

暂无描述 |

|

| ICS932S203AFLNT | IDT |

获取价格 |

Processor Specific Clock Generator, 133.3MHz, PDSO56, 0.300 INCH, GREEN, MO-118, SSOP-56 |

|

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

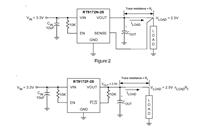

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明