| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CXK79M72C164GB-3 | SONY |

获取价格 |

Standard SRAM, 256KX72, 1.9ns, CMOS, PBGA209, 14 X 22 MM, 1 MM PITCH, PLASTIC, BGA-209 |

|

| CXK79M72C164GB-33 | SONY |

获取价格 |

Standard SRAM, 256KX72, 1.9ns, CMOS, PBGA209, 14 X 22 MM, 1 MM PITCH, PLASTIC, BGA-209 |

|

| CXK79M72C165GB | SONY |

获取价格 |

18Mb 1x1Dp LVCMOS High Speed Synchronous SRAMs (256Kb x 72 or 512Kb x 36) |

|

| CXK79M72C165GB-4 | SONY |

获取价格 |

Standard SRAM, 256KX72, 2.1ns, CMOS, PBGA209, 14 X 22 MM, 1 MM PITCH, PLASTIC, BGA-209 |

|

| CXK79M72C165GB-5 | SONY |

获取价格 |

Standard SRAM, 256KX72, 2.3ns, CMOS, PBGA209, 14 X 22 MM, 1 MM PITCH, PLASTIC, BGA-209 |

|

| CXL-GP | TELEDYNE |

获取价格 |

Small, Low-Cost |

|

| CXL02TG3 | TELEDYNE |

获取价格 |

High Stability |

|

| CXL04GP1 | TELEDYNE |

获取价格 |

High Performance, 1-Axis and 3-Axis Accelerometers |

|

| CXL04GP1Z | TELEDYNE |

获取价格 |

High Performance, 1-Axis and 3-Axis Accelerometers |

|

| CXL04GP3 | TELEDYNE |

获取价格 |

High Performance, 1-Axis and 3-Axis Accelerometers |

|

英伟达Rubin GPU量产或延后:性能飞跃背后的时间博弈

英伟达Rubin GPU量产或延后:性能飞跃背后的时间博弈

外媒爆料:美国秘密在AI芯片中植入追踪器监控中国供应链

外媒爆料:美国秘密在AI芯片中植入追踪器监控中国供应链

中国科学家突破锂电池技术瓶颈:能量密度提升3倍将改写行业格局

中国科学家突破锂电池技术瓶颈:能量密度提升3倍将改写行业格局

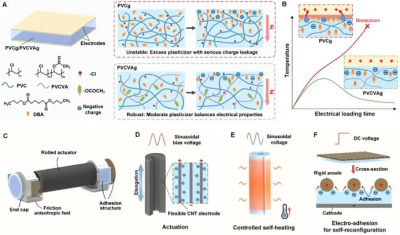

西北工业大学突破极寒技术:抗冻机器人轻松应对-50°C极端环境

西北工业大学突破极寒技术:抗冻机器人轻松应对-50°C极端环境