| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CD74HCT4094E | HARRIS |

获取价格 |

High Speed CMOS Logic 8-Stage Shift and Store Bus Register, Three-State |

|

| CD74HCT4094E | TI |

获取价格 |

High Speed CMOS Logic 8-Stage Shift and Store Bus Register, Three-State |

|

| CD74HCT4094E96 | RENESAS |

获取价格 |

HCT SERIES, 8-BIT RIGHT SERIAL IN PARALLEL OUT SHIFT REGISTER, TRUE OUTPUT, PDIP16, PLASTI |

|

| CD74HCT4094EE4 | TI |

获取价格 |

High-Speed CMOS Logic 8-Stage Shift and Store Bus Register, Three-State |

|

| CD74HCT4094EX | RENESAS |

获取价格 |

IC,SHIFT REGISTER,HCT-CMOS,DIP,16PIN,PLASTIC |

|

| CD74HCT4094H | RENESAS |

获取价格 |

IC,SHIFT REGISTER,HCT-CMOS,DIE |

|

| CD74HCT4094M | HARRIS |

获取价格 |

High Speed CMOS Logic 8-Stage Shift and Store Bus Register, Three-State |

|

| CD74HCT4094M | TI |

获取价格 |

High Speed CMOS Logic 8-Stage Shift and Store Bus Register, Three-State |

|

| CD74HCT4094M | RENESAS |

获取价格 |

SERIAL IN PARALLEL OUT SHIFT REGISTER |

|

| CD74HCT4094M96 | TI |

获取价格 |

High-Speed CMOS Logic 8-Stage Shift and Store Bus Register, Three-State |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

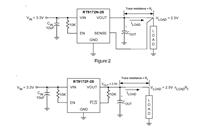

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

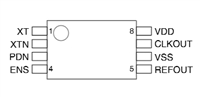

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征