Introduction

•

Five application Universal Asynchronous Receiver-Transmitters (UARTs), up to 3.25 Mbps with

hardware flow control

•

•

•

•

•

•

•

One debug UART operating at up to 115 Kb/s using programmed I/O

2

Two I C master/slave interfaces, up to 400 kbps

Four 32-bit timers and a rotary decoder

Eight Pulse Width Modulators (PWMs)

Real-time clock (RTC)

GPIO with interrupt capability

Power Management Unit (PMU) supports a triple output DC-DC switching converter, multiple

linear regulators, battery charger, and detector.

•

16-channel Low-ResolutionA/D Converter (LRADC). There are 16 physical channels but they can

only be mapped to 8 virtual channels at a time.

•

•

•

•

Single channel High Speed A/D Converter (HSADC), up to 2 Msps data rate

4/5-wire touchscreen controller

Up to 8X8 keypad matrix with button-detect circuit

Security features:

— Read-only unique ID for Digital Rights Management (DRM) algorithms

— Secure boot using 128-bit AES hardware decryption

— SHA-1 and SHA256 hashing hardware

— High assurance boot (HAB4)

•

Offered in 289-pin Ball Grid Array (BGA)

1.2

Ordering Information and Functional Part Differences

Table 1 provides the ordering information for the i.MX28.

Table 1. Ordering Information

Part Number

Projected Temperature Range (°C)

Package

MCIMX280DVM4B

MCIMX280DVM4C

MCIMX280CVM4B

MCIMX280CVM4C

MCIMX283DVM4B

MCIMX283DVM4C

MCIMX283CVM4B

MCIMX283CVM4C

MCIMX286DVM4B

MCIMX286DVM4C

–20 to +70

–20 to +70

–40 to +85

–40 to +85

–20 to +70

–20 to +70

–40 to +85

–40 to +85

–20 to +70

–20 to +70

14 x 14 mm, 0.8mm pitch, MAPBGA-289

14 x 14 mm, 0.8mm pitch, MAPBGA-289

14 x 14 mm, 0.8mm pitch, MAPBGA-289

14 x 14 mm, 0.8mm pitch, MAPBGA-289

14 x 14 mm, 0.8 mm pitch, MAPBGA-289

14 x 14 mm, 0.8 mm pitch, MAPBGA-289

14 x 14 mm, 0.8 mm pitch, MAPBGA-289

14 x 14 mm, 0.8 mm pitch, MAPBGA-289

14 x 14 mm, 0.8 mm pitch, MAPBGA-289

14 x 14 mm, 0.8 mm pitch, MAPBGA-289

i.MX28 Applications Processors for Consumer Products, Rev. 4, 10/2018

NXP Semiconductors

3

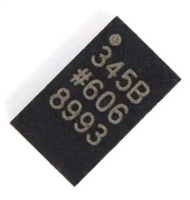

ADXL345传感器工作原理、参数分析、引脚说明

ADXL345传感器工作原理、参数分析、引脚说明

一文带你了解,DAC0832工作原理、输出电压范围、分辨率等参数

一文带你了解,DAC0832工作原理、输出电压范围、分辨率等参数

ACS712电流检测使用指南及资料手册参数分析

ACS712电流检测使用指南及资料手册参数分析

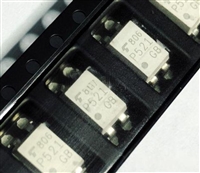

TLP521资料手册解读:参数分析、引脚说明、典型电路

TLP521资料手册解读:参数分析、引脚说明、典型电路