PRELIMINARY

ICS844003I

Integrated

Circuit

Systems, Inc.

FEMTOCLOCKS™ C RYSTAL-TO-LVDS

FREQUENCY SYNTHESIZER

TABLE 1. PIN DESCRIPTIONS

Number

Name

DIV_SELB0

DIV_SELB1

Type

Pulldown

Description

Division select pin for Bank B. Default = Low.

LVCMOS/LVTTL interface levels.

VCO select pin. When Low, the PLL is bypassed and the crystal reference

or TEST_CLK (depending on XTAL_SEL setting) are passed directly to the

output dividers. Has an internal pullup resistor so the PLL is not bypassed

by default. LVCMOS/LVTTL interface levels.

Active HIGH Master Reset. When logic HIGH, the internal dividers are

reset causing the true outputs Qx to go low and the inverted outputs nQx

1

24

Input

Input

2

3

VCO_SEL

Pullup

MR

Input

Pulldown to go high. When logic LOW, the internal dividers and the outputs are

enabled. Has an internal pulldown resistor so the power-up default state of

outputs and dividers are enabled. LVCMOS/LVTTL interface levels.

4

VDDO_A

Power

Ouput

Output supply pin for Bank A outputs.

5, 6

QA0, nQA0

Differential output pair. LVDS interface levels.

Output enable Bank B. Active High outputs are enable. When logic HIGH,

the output pairs on Bank B are enabled. When logic LOW, the output pairs

are in a high impedance state. Has an internal pullup resistor so the default

7

OEB

Input

Pullup

power-up state of outputs are enabled. LVCMOS/LVTTL interface levels.

Output enable Bank A. Active High output enable. When logic HIGH,

the output pair in Bank A is enabled. When logic LOW, the output pair is in

Pullup

8

9

OEA

Input

Input

a high impedance state. Has an internal pullup resistor so the default

power-up state of output is enabled. LVCMOS/LVTTL interface levels.

Feedback divide select. When Low (default), the feedback divider is set

Pulldown for ÷20. When HIGH, the feedback divider is set for ÷24.

LVCMOS/LVTTL interface levels.

FB_DIV

10

11

VDDA

VDD

Power

Power

Analog supply pin.

Core supply pin.

12

13

DIV_SELA0

DIV_SELA1

Division select pin for Bank A. Default = HIGH.

Pullup

Input

LVCMOS/LVTTL interface levels.

14

GND

Power

Power supply ground.

Parallel resonant crystal interface. XTAL_OUT is the output, XTAL_IN is the

input. XTAL_IN is also the overdrive pin if you want to overdrive the crystal

circuit with a single-ended reference clock.

XTAL_OUT,

XTAL_IN

15, 16

Input

Input

Input

Single-ended reference clock input. Has an internal pulldown resistor to

Pulldown pull to low state by default. Can leave floating if using the crystal interface.

LVCMOS/LVTTL interface levels.

17

18

TEST_CLK

XTAL_SEL

Crystal select pin. Selects between the single-ended TEST_CLK or crystal

interface. Has an internal pullup resistor so the crystal interface is selected

by default. LVCMOS/LVTTL interface levels.

Pullup

19, 20

21, 22

23

nQB1, QB1 Output

Differential output pair. LVDS interface levels.

Differential output pair. LVDS interface levels.

Output supply pin for Bank B outputs.

nQB0, QB0

VDDO_B

Output

Power

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

TABLE 2. PIN CHARACTERISTICS

Symbol

Parameter

Test Conditions

Minimum

Typical

Maximum Units

CIN

Input Capacitance

4

pF

kΩ

kΩ

RPULLDOWN Input Pulldown Resistor

51

51

RPULLUP

Input Pullup Resistor

844003AGI

www.icst.com/products/hiperclocks.html

REV.C APRIL 12, 2006

2

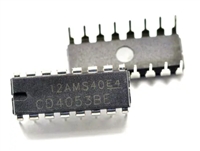

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南

TLP250光耦合器:资料手册参数分析

TLP250光耦合器:资料手册参数分析