| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 74LS112B | NXP |

获取价格 |

J-K Flip-Flop, LS Series, 2-Func, Negative Edge Triggered, 2-Bit, Complementary Output, TT |

|

| 74LS112DC | ETC |

获取价格 |

J-K-Type Flip-Flop |

|

| 74LS112DCQR | FAIRCHILD |

获取价格 |

J-K Flip-Flop, 2-Func, Negative Edge Triggered, TTL, CDIP16, |

|

| 74LS112F | NXP |

获取价格 |

IC LS SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16, CE |

|

| 74LS112N | RAYTHEON |

获取价格 |

J-K Flip-Flop, 2-Func, Negative Edge Triggered, TTL, PDIP16, |

|

| 74LS112PC | ETC |

获取价格 |

J-K-Type Flip-Flop |

|

| 74LS112PCQR | FAIRCHILD |

获取价格 |

暂无描述 |

|

| 74LS113A | NXP |

获取价格 |

LS SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDIP14 |

|

| 74LS113AD | ROCHESTER |

获取价格 |

J-K Flip-Flop |

|

| 74LS113DCQR | FAIRCHILD |

获取价格 |

Jbar-Kbar Flip-Flop, 2-Func, Negative Edge Triggered, TTL, CDIP14, |

|

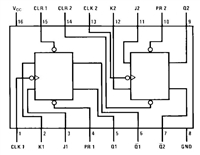

74LS112引脚图及功能表详解

74LS112引脚图及功能表详解

国产厂商思特威CMOS图像传感器芯片单月出货超1亿颗,技术创新引领行业发展

国产厂商思特威CMOS图像传感器芯片单月出货超1亿颗,技术创新引领行业发展

台积电5nm和3nm产能利用率达100%,半导体行业景气度持续攀升

台积电5nm和3nm产能利用率达100%,半导体行业景气度持续攀升

AMD宣布全球裁员约1000人,调整战略聚焦增长

AMD宣布全球裁员约1000人,调整战略聚焦增长