74LS112是一种双非门J-K触发器。它由两个独立的J-K触发器组成。J-K触发器具有三个输入端,分别为J、K和CLK。当CLK为高电平时,如果J和K的电平状态相同,则输出不变。如果J和K的电平状态不同,则输出将取反。当CLK为低电平时,输入和输出之间没有关系。

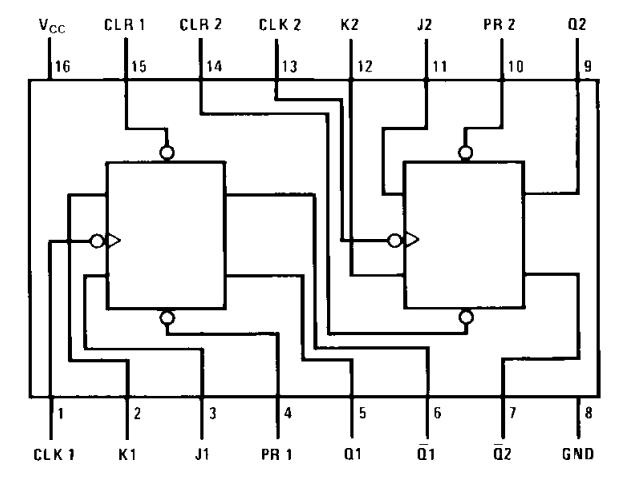

74LS112引脚图

CLK1、CLK2————时钟输入端(下降沿有用)

J1、J2、K1、K2————数据输入端

Q1、Q2、/Q1、/Q2————输出端

CLR1、CLR2————直接复位端(低电平有用)

PR1、PR2————直接置位端(低电平有用)

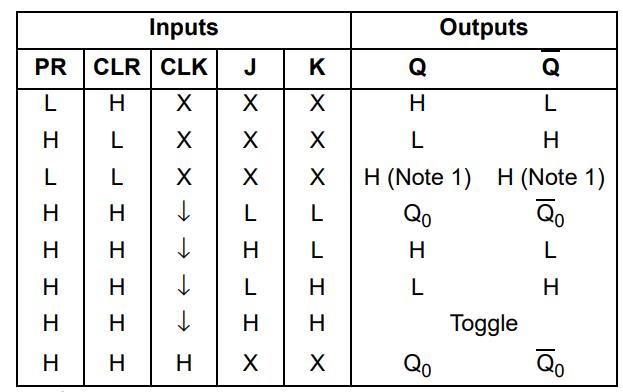

74LS112功用表

阐述:

H-高电平

L-低电平

X-恣意

↓-高到低电平跳变

Q0-稳态输入树立前 Q 的电平

/Q0-稳态输入树立前/Q 的电平

浙公网安备 33010502006866号

浙公网安备 33010502006866号