74LS161是一个同步的可预置的四位二进制计数器,并自带有异步功能。可以采用反馈归零法进行6进制的计数器设计。

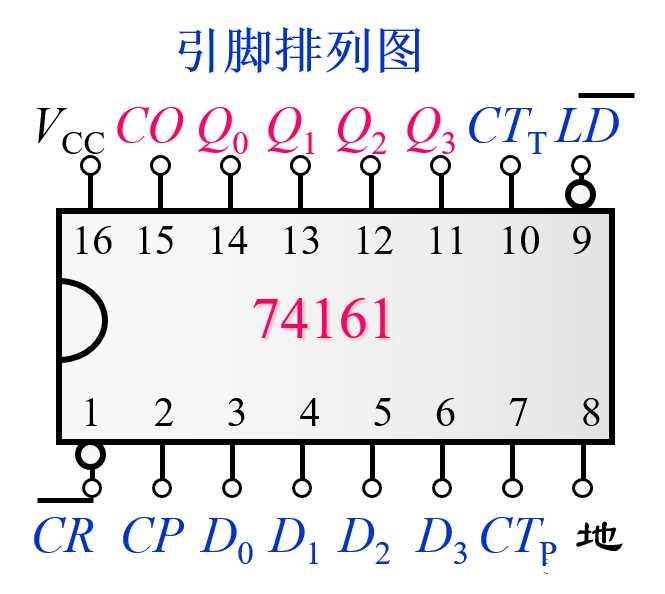

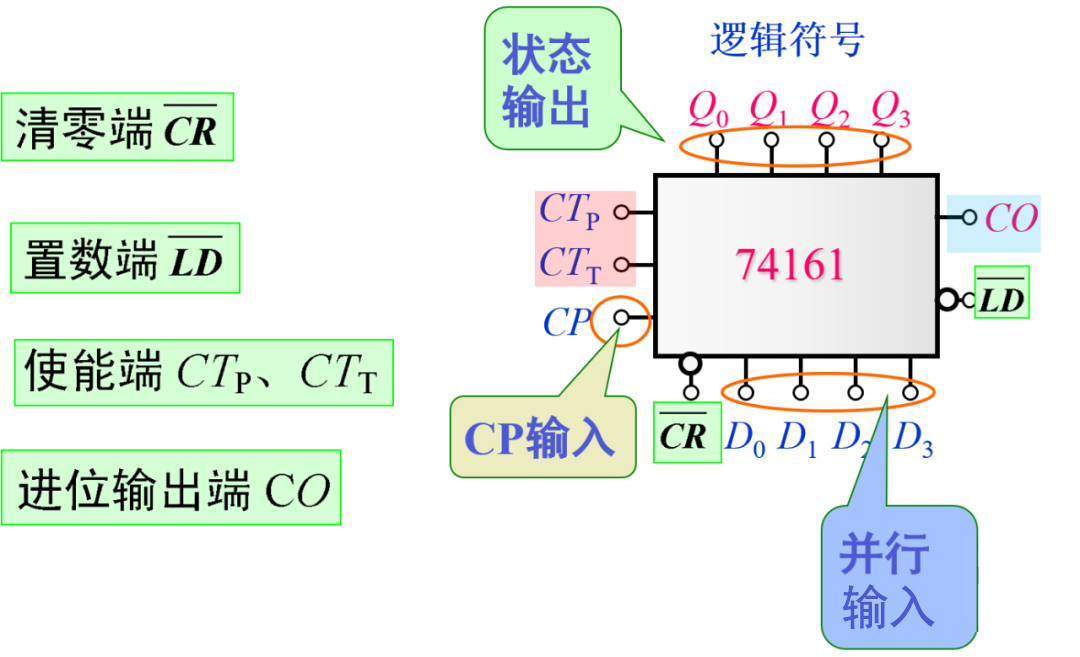

74LS161引脚图及介绍:

1脚:RD'为清零端,低电平有效。

2脚:CP为时钟脉冲输入端,上升沿有效。

3~6脚:A0~A3为输入(预置)端,可预置任意一个4位二进制数。

7,10脚:EP,ET为为计数控制端,两脚同时为高电平时芯片计数;任意一脚为低电平时计数器保持原数据。

9脚:LD'为并行(寄存器)启用控制端,低电平有效。

11~14脚:Q0~Q3为数据输出端。

15脚:RCO为进位输出端(满16进一),高电平有效。

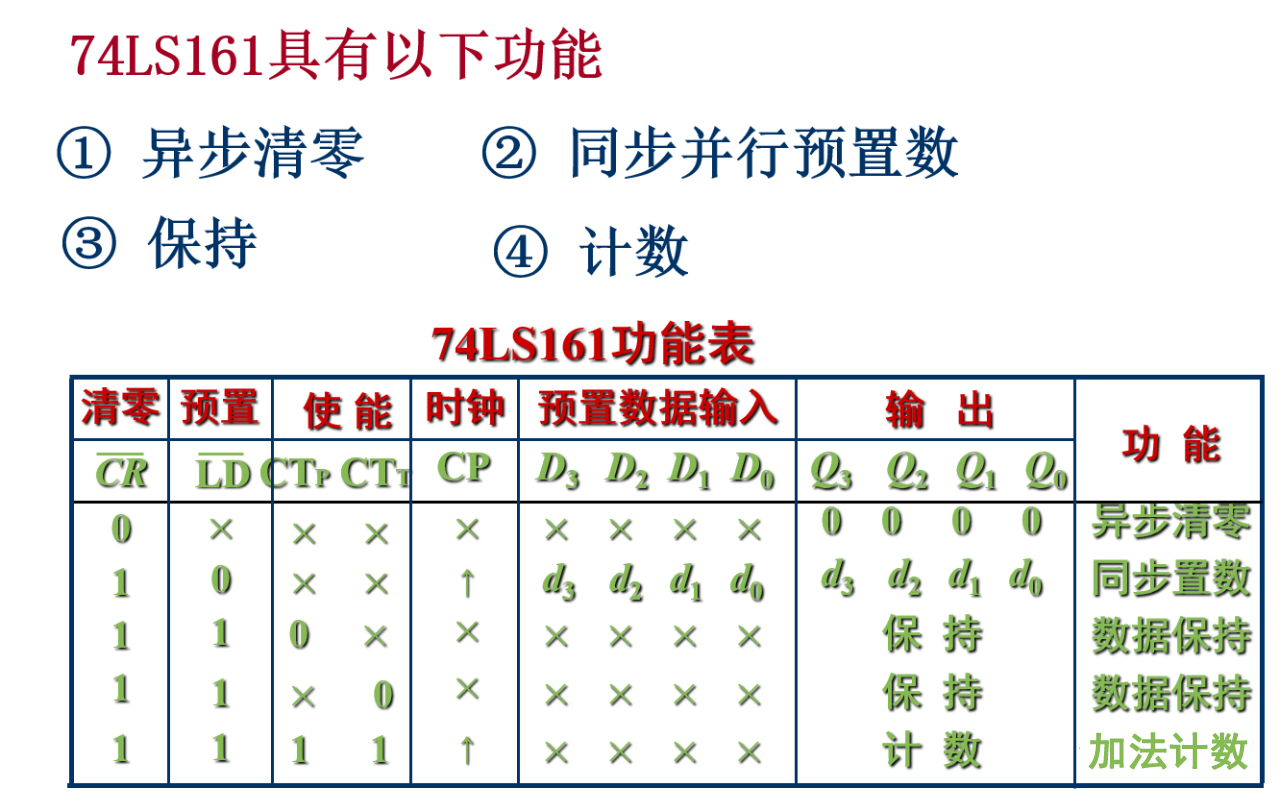

74LS161的功能:

1)清零

CR’端为异步清零端,只要CR’=0,触发器被清零,计数器输出全为0,不需要等CP的时钟信号即可实现清零功能。

2)置数控制端

LD’为同步并行置入控制端(低电平有效),当CR’=1,LD‘=0,在时钟脉冲CP的上升沿时,将D0 ~ D3置入Q0 ~ Q3。

3)保持

在CTt和CTp做与运算结果为0(只要有一个为0)计数器就处于保持功能。

当CTt=0时,触发器保持且C0=0。

(计数器控制端CTT、CTp和输出端是为了级联而设置的。)

4)计数

当CR’=1,LD’=1,CTt=1,CTp=1均满足时,在时钟脉冲的上升沿,触发器开始计数功能。

其功能表如下表所示:

在实际应用中,我们常常使用集成计数器。本文章介绍74LS161(二-十六进制计数器),其具有计数、保持、异步清零、同步置数共四种功能。

959

959

浙公网安备 33010502006866号

浙公网安备 33010502006866号