| 是否Rohs认证: | 符合 | 生命周期: | Obsolete |

| 零件包装代码: | TO-220AB | 包装说明: | PLASTIC, SC-46, 3 PIN |

| 针数: | 3 | Reach Compliance Code: | unknown |

| ECCN代码: | EAR99 | 风险等级: | 5.83 |

| 雪崩能效等级(Eas): | 60 mJ | 外壳连接: | DRAIN |

| 配置: | SINGLE WITH BUILT-IN DIODE | 最小漏源击穿电压: | 25 V |

| 最大漏极电流 (Abs) (ID): | 55 A | 最大漏极电流 (ID): | 55 A |

| 最大漏源导通电阻: | 0.018 Ω | FET 技术: | METAL-OXIDE SEMICONDUCTOR |

| JEDEC-95代码: | TO-220AB | JESD-30 代码: | R-PSFM-T3 |

| JESD-609代码: | e3 | 元件数量: | 1 |

| 端子数量: | 3 | 工作模式: | ENHANCEMENT MODE |

| 最高工作温度: | 175 °C | 封装主体材料: | PLASTIC/EPOXY |

| 封装形状: | RECTANGULAR | 封装形式: | FLANGE MOUNT |

| 峰值回流温度(摄氏度): | NOT SPECIFIED | 极性/信道类型: | N-CHANNEL |

| 最大功率耗散 (Abs): | 85 W | 最大脉冲漏极电流 (IDM): | 220 A |

| 认证状态: | Not Qualified | 子类别: | FET General Purpose Power |

| 表面贴装: | NO | 端子面层: | Matte Tin (Sn) |

| 端子形式: | THROUGH-HOLE | 端子位置: | SINGLE |

| 处于峰值回流温度下的最长时间: | NOT SPECIFIED | 晶体管应用: | SWITCHING |

| 晶体管元件材料: | SILICON | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| PHP55N03LTA | NXP |

获取价格 |

N-channel enhancement mode field-effect transistor |

|

| PHP55N03T | NXP |

获取价格 |

TrenchMOS transistor Standard level FET |

|

| PHP55N04LT | ETC |

获取价格 |

TRANSISTOR | MOSFET | N-CHANNEL | 35V V(BR)DSS | 55A I(D) | TO-220AB |

|

| PHP5N20E | NXP |

获取价格 |

PowerMOS transistor |

|

| PHP5N40 | NXP |

获取价格 |

PowerMOS transistor |

|

| PHP5N40E | NXP |

获取价格 |

PowerMOS transistor |

|

| PHP60 | MICROSEMI |

获取价格 |

TRANSIENT ABSORPTION ZENER |

|

| PHP60 | SEMTECH |

获取价格 |

7,500 & 15,000 Watt TVS Module |

|

| PHP60 | PROTEC |

获取价格 |

AC POWER BUS VOLTAGE SUPPRESSOR |

|

| PHP60 | SENSITRON |

获取价格 |

Transient Voltage Suppressor, Unidirectional |

|

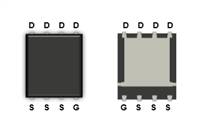

STS5DNE30L资料手册解读:参数分析、特性与应用

STS5DNE30L资料手册解读:参数分析、特性与应用

MDU1511资料手册解读:探索这款MOSFET的全面特性

MDU1511资料手册解读:探索这款MOSFET的全面特性

2SB1260资料手册解读:电气参数、产品特性

2SB1260资料手册解读:电气参数、产品特性

掌握电感选型:关键参数Q值全解析

掌握电感选型:关键参数Q值全解析