| 是否Rohs认证: | 符合 | 生命周期: | Active |

| 包装说明: | LFQFP, | Reach Compliance Code: | compliant |

| HTS代码: | 8542.39.00.01 | 风险等级: | 1.1 |

| Samacsys Confidence: | 4 | Samacsys Status: | Released |

| Samacsys PartID: | 938013 | Samacsys Pin Count: | 48 |

| Samacsys Part Category: | Integrated Circuit | Samacsys Package Category: | Quad Flat Packages |

| Samacsys Footprint Name: | 48 LEAD LQFP_1 | Samacsys Released Date: | 2018-05-22 10:38:35 |

| Is Samacsys: | N | JESD-30 代码: | S-PQFP-G48 |

| JESD-609代码: | e3 | 长度: | 7 mm |

| 功能数量: | 1 | 端子数量: | 48 |

| 最高工作温度: | 70 °C | 最低工作温度: | |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | LFQFP |

| 封装形状: | SQUARE | 封装形式: | FLATPACK, LOW PROFILE, FINE PITCH |

| 峰值回流温度(摄氏度): | NOT SPECIFIED | 座面最大高度: | 1.6 mm |

| 标称供电电压: | 1.8 V | 表面贴装: | YES |

| 电信集成电路类型: | LAN SWITCHING CIRCUIT | 温度等级: | COMMERCIAL |

| 端子面层: | Matte Tin (Sn) - annealed | 端子形式: | GULL WING |

| 端子节距: | 0.5 mm | 端子位置: | QUAD |

| 处于峰值回流温度下的最长时间: | NOT SPECIFIED | 宽度: | 7 mm |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 替代类型 | 描述 | 数据表 |

| KSZ8863FLLI | MICROCHIP |

类似代替  |

Integrated 3-Port 10/100 Managed Switch with PHYs |

|

| KSZ8863RLLI | MICROCHIP |

类似代替  |

DATACOM, LAN SWITCHING CIRCUIT, PQFP48 |

|

| KSZ8863MLLI | MICROCHIP |

类似代替  |

DATACOM, LAN SWITCHING CIRCUIT, PQFP48 |

|

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| KSZ8863RLLI | MICROCHIP |

获取价格 |

DATACOM, LAN SWITCHING CIRCUIT, PQFP48 |

|

| KSZ8863RLLITR | MICROCHIP |

获取价格 |

Integrated 3-Port 10/100 Managed Switch with PHYs |

|

| KSZ8863RLLI-TR | MICROCHIP |

获取价格 |

Integrated 3-Port 10/100 Managed Switch with PHYs |

|

| KSZ8863RLLTR | MICROCHIP |

获取价格 |

Integrated 3-Port 10/100 Managed Switch with PHYs |

|

| KSZ8863RLL-TR | MICROCHIP |

获取价格 |

Integrated 3-Port 10/100 Managed Switch with PHYs |

|

| KSZ8864 | MICROCHIP |

获取价格 |

The KSZ8864 is a highly-integrated, Layer 2 managed 4-port switch with optimized design, p |

|

| KSZ8864CNX | MICROCHIP |

获取价格 |

Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces |

|

| KSZ8864CNXC | MICROCHIP |

获取价格 |

Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces |

|

| KSZ8864CNXC-TR | MICROCHIP |

获取价格 |

IC SWITCH 4 PORT MII/RMII 64QFN |

|

| KSZ8864CNXI | MICROCHIP |

获取价格 |

IC ETHERNET SWITCH 4PORT 64QFN |

|

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

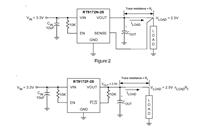

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明