| 品牌 | Logo | 应用领域 |

| 美国微芯 - MICROCHIP | 局域网(LAN)标准以太网:16GBASE-T电信电信集成电路 | |

| 页数 | 文件大小 | 规格书 |

| 96页 | 1237K |  |

| 描述 | ||

| IC ETHERNET SWITCH 4PORT 64QFN | ||

| 是否无铅: | 不含铅 | 是否Rohs认证: | 符合 |

| 生命周期: | Active | 包装说明: | HVQCCN, LCC64,.32SQ,16 |

| Reach Compliance Code: | compliant | Factory Lead Time: | 17 weeks |

| 风险等级: | 2.34 | Samacsys Description: | Ethernet ICs 4-Port 10/100 Switch w/ 2x MAC I/F, MII, RMII |

| 其他特性: | SEATED HT-CALCULATED | 数据速率: | 100000 Mbps |

| JESD-30 代码: | S-XQCC-N64 | JESD-609代码: | e3 |

| 长度: | 8 mm | 湿度敏感等级: | 3 |

| 功能数量: | 1 | 端子数量: | 64 |

| 收发器数量: | 2 | 最高工作温度: | 85 °C |

| 最低工作温度: | -40 °C | 封装主体材料: | UNSPECIFIED |

| 封装代码: | HVQCCN | 封装等效代码: | LCC64,.32SQ,16 |

| 封装形状: | SQUARE | 封装形式: | CHIP CARRIER, HEAT SINK/SLUG, VERY THIN PROFILE |

| 峰值回流温度(摄氏度): | 260 | 座面最大高度: | 0.9 mm |

| 标称供电电压: | 1.2 V | 表面贴装: | YES |

| 电信集成电路类型: | ETHERNET TRANSCEIVER | 温度等级: | INDUSTRIAL |

| 端子面层: | Matte Tin (Sn) - annealed | 端子形式: | NO LEAD |

| 端子节距: | 0.4 mm | 端子位置: | QUAD |

| 处于峰值回流温度下的最长时间: | 30 | 宽度: | 8 mm |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| KSZ8864CNXIA | MICROCHIP |

获取价格 |

Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces |

|

| KSZ8864CNXIA-TR | MICROCHIP |

获取价格 |

暂无描述 |

|

| KSZ8864CNXI-TR | MICROCHIP |

获取价格 |

IC SWITCH 4 PORT MII/RMII 64QFN |

|

| KSZ8864RMN | MICREL |

获取价格 |

Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces |

|

| KSZ8864RMNC-TR | MICROCHIP |

获取价格 |

Ethernet Transceiver, QCC64 |

|

| KSZ8864RMNI | MICREL |

获取价格 |

Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces |

|

| KSZ8864RMNUB | MICROCHIP |

获取价格 |

DATACOM, ETHERNET TRANSCEIVER, QCC64 |

|

| KSZ8864RMNUB-TR | MICROCHIP |

获取价格 |

IC ETHERNET SWITCH 4PORT |

|

| KSZ8864RMNUB-TR-VAO | MICROCHIP |

获取价格 |

Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces |

|

| KSZ8864RMNUB-VAO | MICROCHIP |

获取价格 |

Ethernet Transceiver, QCC64 |

|

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

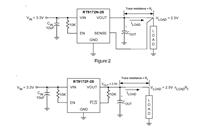

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明