| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| IDT723653L15PF9 | IDT |

获取价格 |

FIFO, 2KX36, 10ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

| IDT723653L15PFG | IDT |

获取价格 |

FIFO, 2KX36, 10ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

| IDT723653L15PFG8 | IDT |

获取价格 |

FIFO, 2KX36, 10ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

| IDT723653L20PF | IDT |

获取价格 |

FIFO, 2KX36, 12ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

| IDT723654 | IDT |

获取价格 |

CMOS SyncBiFIFO WITH BUS-MATCHING |

|

| IDT723654L12PF | IDT |

获取价格 |

CMOS SyncBiFIFO WITH BUS-MATCHING |

|

| IDT723654L12PFG | IDT |

获取价格 |

FIFO, 2KX36, 8ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

| IDT723654L15PF | IDT |

获取价格 |

CMOS SyncBiFIFO WITH BUS-MATCHING |

|

| IDT723654L15PFG | IDT |

获取价格 |

FIFO, 2KX36, 10ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

| IDT723654L15PFG8 | IDT |

获取价格 |

FIFO, 2KX36, 10ns, Synchronous, CMOS, PQFP128, TQFP-128 |

|

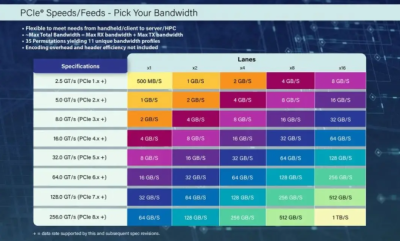

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

寒武纪紧急辟谣背后:AI芯片龙头的真实现状与投资陷阱

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

英伟达50亿入股英特尔:芯片巨头联手剑指AMD,行业格局生变

闪迪预警:NAND闪存供应短缺将持续至2026年

闪迪预警:NAND闪存供应短缺将持续至2026年