| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| GM76V8128CLST-85E | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLST-85I | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT1-70 | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT1-70E | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT1-70I | HYNIX |

获取价格 |

Standard SRAM, 128KX8, 70ns, CMOS, PDSO32 |

|

| GM76V8128CLT1-85 | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT1-85E | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT1-85I | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT-70 | ETC |

获取价格 |

x8 SRAM |

|

| GM76V8128CLT-85 | ETC |

获取价格 |

x8 SRAM |

|

压敏电阻与气体放电管串联使用的专业解析

压敏电阻与气体放电管串联使用的专业解析

手册解读:MMBT3904参数与管脚图及代换

手册解读:MMBT3904参数与管脚图及代换

74LS298PC手册解读:参数说明、引脚说明、替代型号推荐

74LS298PC手册解读:参数说明、引脚说明、替代型号推荐

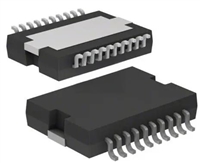

L6234手册解读:引脚信息、电气参数

L6234手册解读:引脚信息、电气参数