| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| EVAL-ADN4650EB1Z | ADI |

获取价格 |

EVAL BOARD FOR ADN4650 |

|

| EVAL-ADN4650EBZ | ADI |

获取价格 |

EVAL BOARD FOR ADN4650 |

|

| EVAL-ADN4651EB1Z | ADI |

获取价格 |

5 kV RMS, 600 Mbps, Dual-Channel LVDS Isolators |

|

| EVAL-ADN4652EB1Z | ADI |

获取价格 |

5 kV RMS, 600 Mbps, Dual-Channel LVDS Isolators |

|

| EVAL-ADN4654EB1Z | ADI |

获取价格 |

5 kV RMS and 3.75 kV RMS, Dual-Channel LVDS Gigabit Isolators |

|

| EVAL-ADN4655EB1Z | ADI |

获取价格 |

5 kV RMS and 3.75 kV RMS, Dual-Channel LVDS Gigabit Isolators |

|

| EVAL-ADN4656EB1Z | ADI |

获取价格 |

5 kV RMS and 3.75 kV RMS, Dual-Channel LVDS Gigabit Isolators |

|

| EVAL-ADN469XEFDEBZ | ADI |

获取价格 |

3.3 V, 200 Mbps, Half- and Full-Duplex |

|

| EVAL-ADN469XEHDEBZ | ADI |

获取价格 |

3.3 V, 200 Mbps, Half- and Full-Duplex |

|

| EVAL-ADP1712 | ADI |

获取价格 |

evaluation boards |

|

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

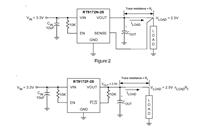

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明