5 kV RMS/3.75 kV RMS, 600 Mbps,

Dual-Channel LVDS Isolators

Data Sheet

ADN4650/ADN4651/ADN4652

FEATURES

FUNCTIONAL BLOCK DIAGRAMS

V

V

IN1

IN2

5 kV rms/3.75 kV rms LVDS isolator

ADN4650

Complies with TIA/EIA-644-A LVDS standard

Multiple dual-channel configurations

Up to 600 Mbps switching with low jitter

4.5 ns maximum propagation delay

ISOLATION

BARRIER

LDO

LDO

V

D

V

DD2

DD1

D

D

IN1+

IN1–

OUT1+

OUT1–

D

151 ps maximum peak-to-peak total jitter at 600 Mbps

100 ps maximum pulse skew

600 ps maximum part to part skew

LVDS

DIGITAL ISOLATOR

LVDS

D

D

D

D

IN2+

OUT2+

OUT2–

IN2–

2.5 V or 3.3 V supplies

GND

GND

2

1

−75 dBc power supply ripple rejection and glitch immunity

8 kV IEC 61000-4-2 ESD protection across isolation barrier

High common-mode transient immunity: >25 kV/μs

Passes EN55022 Class B radiated emissions limits with

600 Mbps PRBS

Safety and regulatory approvals (20-lead SOIC package)

UL: 5000 V rms for 1 minute per UL 1577

CSA Component Acceptance Notice 5A

VDE certificate of conformity

Figure 1.

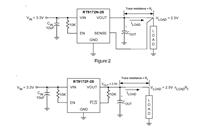

V

V

IN2

IN1

ADN4651

ISOLATION

BARRIER

LDO

LDO

V

D

V

DD2

DD1

D

D

IN1+

IN1–

OUT1+

OUT1–

D

LVDS

DIGITAL ISOLATOR

LVDS

D

D

D

D

OUT2+

IN2+

IN2–

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

VIORM = 424 V peak

OUT2–

Fail-safe output high for open, short, and terminated input

conditions (ADN4651/ADN4652)

Operating temperature range: −40°C to +125°C

Choice of package and isolation options

3.75 kV rms in highly integrated 20-lead SSOP

5 kV rms in 20-lead SOIC with 7.8 mm creepage/clearance

GND

GND

2

1

Figure 2.

V

V

IN1

IN2

ADN4652

ISOLATION

BARRIER

LDO

LDO

V

V

DD2

DD1

D

D

APPLICATIONS

D

D

IN1+

OUT1+

OUT1–

IN1–

Analog front-end (AFE) isolation

LVDS

DIGITAL ISOLATOR

LVDS

Data plane isolation

Isolated high speed clock and data links

Isolated serial peripheral interface (SPI) over LVDS

D

D

D

OUT2+

IN2+

D

OUT2–

IN2–

GND

GND

2

1

GENERAL DESCRIPTION

Figure 3.

The ADN4650/ADN4651/ADN46521 are signal isolated, low

voltage differential signaling (LVDS) buffers that operate at up

to 600 Mbps with very low jitter.

ensure a Logic 1 on the corresponding LVDS driver output

when the inputs are floating, shorted, or terminated, but not

driven.

The devices integrate Analog Devices, Inc., iCoupler® technology,

enhanced for high speed operation, to provide galvanic isolation of

the TIA/EIA-644-A compliant LVDS drivers and receivers.

This technology allows drop-in isolation of an LVDS signal

chain.

For high speed operation with low jitter, the LVDS and isolator

circuits rely on a 2.5 V supply. An integrated on-chip low dropout

regulator (LDO) can provide the required 2.5 V from an external

3.3 V power supply. The devices are fully specified over a wide

industrial temperature range and are available in a 20-lead,

wide body SOIC package with 5 kV rms isolation or a 20-lead

SSOP package with 3.75 kV rms isolation.

Multiple channel configurations are offered, and the LVDS receivers

on the ADN4651/ADN4652 include a fail-safe mechanism to

1 Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329. Other patents are pending.

Rev. E Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registeredtrademarks arethe property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2015–2019 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明