CYWB022XX Family

P-Port of the WLCSP package only supports PNAND and SPI

interface.

Functional Overview

Turbo-MTP Support

The memory address is decoded to access any of the multiple

endpoint buffers inside Astoria. These endpoints serve as buffers

for data between each pair of ports, for example, between the

processor port and the USB port. The processor writes and reads

into these buffers through the memory interface.

Turbo-MTP is an implementation of Microsoft’s MTP enabled by

West Bridge. In the current generation of MTP-enabled mobile

phones, all protocol packets needs to be handled by the main

processor. West Bridge Turbo-MTP switches these packet types

and sends only control packets to the processor, while data

payloads are written directly to mass storage, thereby bringing

the high performance of West Bridge to MTP. For more

information refer to the application note Optimizing Performance

using West Bridge® Controllers with Turbo-MTP.

Access to these buffers is controlled by either using a DMA

protocol or using an interrupt to the main processor. These two

modes are configurable by the external processor. The 81-ball

WLCSP package only supports interrupt.

As a DMA slave, Astoria generates a DMA request signal to

signify to the main processor that a specific buffer is ready to be

read from or written to. The external processor monitors this

signal and polls Astoria for the specific buffers ready for read or

write. It then performs the appropriate read or write operations

on the buffer through the processor interface. This way, the

external processor only deals with the buffers to access a

multitude of storage devices connected to Astoria.

SLIM Architecture

The SLIM architecture enables three different interfaces (P-port,

S-port, and U-port) to connect to one another independently.

With this architecture, connecting a device using Astoria to a PC

through USB does not disturb any of the functions of the device.

The device can still access mass storage at the same time as the

PC synchronizes with the main processor.

In the interrupt mode, Astoria communicates important buffer

status changes to the external processor using an interrupt

signal. The external processor then polls Astoria for the specific

buffers ready for read or write and it performs the appropriate

read or write operations through the processor interface.

The SLIM architecture enables new usage models in which a PC

can access a mass storage device independent of the main

processor or enumerate access to both the mass storage and

the main processor at the same time.

In a handset, this typically enables using the phone as a thumb

drive, downloading media files to the phone while still having full

functionality available on the phone, or using the same phone as

a modem to connect the PC to the web.

FlexBoot

FlexBoot is an optional feature that Astoria emulates a NAND

Flash device. In this optional feature, the P-Port is configured as

pseudo NAND interface. The processor can download its boot

image through the P-Port.

8051 Microprocessor

When P-Port is configured to pseudo NAND interface, it supports

two operation modes:

The 8051 microprocessor embedded in Astoria does basic

transaction management for all the transactions between P-Port,

S-Port, and U-Port. The 8051 does not reside in the data path; it

manages the path. The data path is optimized for performance.

The 8051 executes firmware that supports SD, SDIO, MMC+,

and CE-ATA devices at the S-Port.

■ Logic NAND Access (LNA) mode

■ Non-Logic NAND Access (non-LNA) mode

LNA refers to the mode of operation where Astoria emulates a

NAND flash device. This mode is designed for systems that

require booting of the system processor from a NAND Flash

device. In this type of application, the system processor can

communicate to Astoria using common NAND commands to

boot from a NAND Flash connected to Astoria’s S-port. In this

mode of operation, Astoria mimics a real NAND device and

allows the system processor to use its internal boot-ROM to boot

from Astoria, as it boots from a NAND Flash.

Configuration and Status Registers

The West Bridge Astoria device includes configuration and

status registers that are accessible as memory mapped registers

through the processor interface. The configuration registers

allow the system to specify certain Astoria behaviors. For

example, it is able to mask certain status registers from raising

an interrupt. The status registers convey various status such as

the addresses of buffers for read operations.

In the non-LNA mode of operation, the system processor

interfaces with Astoria using standard NAND interface, but does

not use standard NAND commands. In this mode, Astoria

responds to a subset of NAND commands. The system

processor uses a set of APIs provided by Cypress to

communicate through its NAND controller to Astoria. For details,

refer to the application note “Interfacing To West Bridge™

Astoria’s™ Pseudo-NAND Processor Port“.

Processor Interface (P-Port)

Communication with the external processor is realized through a

dedicated processor interface. This interface is configured to

support different interface standards. This interface supports

multiplexing and nonmultiplexing address or data bus in both

synchronous and asynchronous pseudo CRAM-mapped, and

nonmultiplexing address or data asynchronous SRAM-mapped

memory accesses. The interface also can be configured to a

pseudo NAND interface to support the processor’s NAND

interface. In addition, this interface can be configured to support

SPI slave. Asynchronous accesses can reach a bandwidth of up

to 66.7 MBps. Synchronous accesses can be performed at

33 MHz across 16 bits for up to 66.7 MBps bandwidth. The

USB Interface (U-Port)

In accordance with the USB 2.0 specification, Astoria can

operate in both full speed and high speed USB modes. The USB

interface consists of the USB transceiver and can be accessed

by both the P-Port and the S-Port.

Document Number: 001-13805 Rev. *M

Page 3 of 78

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

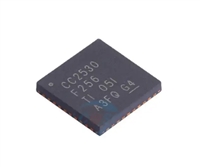

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

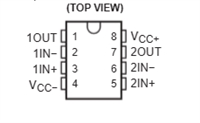

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析