| 生命周期: | Active | 包装说明: | , |

| Reach Compliance Code: | unknown | 风险等级: | 5.62 |

| uPs/uCs/外围集成电路类型: | MICROPROCESSOR CIRCUIT | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| CYWB0224ABS-BVXIES | CYPRESS | West Bridge®: Astoria⢠USB and Mass Storag |

获取价格 |

|

| CYWB0224ABS-BVXIT | CYPRESS | West Bridge®: Astoria⢠USB and Mass Storag |

获取价格 |

|

| CYWB0224ABS-BZXI | CYPRESS | West Bridge®: Astoria⢠USB and Mass Storag |

获取价格 |

|

| CYWB0224ABSX-FDXI | CYPRESS | West Bridge®: Astoria⢠USB and Mass Storag |

获取价格 |

|

| CYWB0224ABSX-FDXIT | CYPRESS | West Bridge®: Astoria⢠USB and Mass Storag |

获取价格 |

|

| CYWB0226ABS-BVXI | CYPRESS | West Bridge®: Astoria⢠USB and Mass Storag |

获取价格 |

|

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

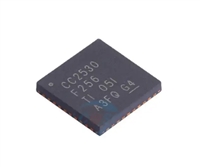

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

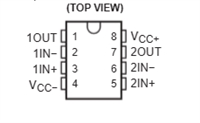

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析