| 是否无铅: | 不含铅 | 是否Rohs认证: | 符合 |

| 生命周期: | Transferred | 零件包装代码: | BGA |

| 包装说明: | LBGA, | 针数: | 256 |

| Reach Compliance Code: | compliant | HTS代码: | 8542.39.00.01 |

| 风险等级: | 5.33 | Is Samacsys: | N |

| JESD-30 代码: | S-PBGA-B256 | JESD-609代码: | e1 |

| 长度: | 17 mm | 可配置逻辑块数量: | 2304 |

| 等效关口数量: | 40000 | 端子数量: | 256 |

| 最高工作温度: | 70 °C | 最低工作温度: | |

| 组织: | 2304 CLBS, 40000 GATES | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | LBGA | 封装形状: | SQUARE |

| 封装形式: | GRID ARRAY, LOW PROFILE | 峰值回流温度(摄氏度): | 260 |

| 可编程逻辑类型: | FIELD PROGRAMMABLE GATE ARRAY | 认证状态: | Not Qualified |

| 座面最大高度: | 1.5 mm | 最大供电电压: | 3.6 V |

| 最小供电电压: | 3 V | 标称供电电压: | 3.3 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | COMMERCIAL | 端子面层: | TIN SILVER COPPER |

| 端子形式: | BALL | 端子节距: | 1 mm |

| 端子位置: | BOTTOM | 处于峰值回流温度下的最长时间: | 40 |

| 宽度: | 17 mm | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| AT95202G41221Y | MERITEK |

获取价格 |

AT95202G41221Y | 2.4GHz 1W RF Ceramic Chip An |

|

| AT95N08S | ANBON |

获取价格 |

TO-220AB |

|

| AT970 | POSEICO |

获取价格 |

PHASE CONTROL THYRISTOR |

|

| AT970S34 | POSEICO |

获取价格 |

PHASE CONTROL THYRISTOR |

|

| AT971 | POSEICO |

获取价格 |

PHASE CONTROL THYRISTOR |

|

| AT971S42 | POSEICO |

获取价格 |

PHASE CONTROL THYRISTOR |

|

| AT975 | POSEICO |

获取价格 |

PHASE CONTROL THYRISTOR |

|

| AT975S52 | POSEICO |

获取价格 |

PHASE CONTROL THYRISTOR |

|

| AT97SC3201 | ATMEL |

获取价格 |

Trusted Platform Module |

|

| AT97SC3201-01AC | ATMEL |

获取价格 |

Trusted Platform Module |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

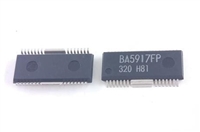

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐