在嵌入式系统的应用开发领域,实现复杂的分立逻辑功能一直是开发者面临的挑战之一。不过,Microchip推出的PIC16F13145系列单片机为解决这一问题带来了新的思路和方法。开发人员能够利用该系列单片机中的可配置逻辑模块(CLB)外设,实现硬件中复杂的分立逻辑功能,进而精简物料清单(BOM)并开发定制专用逻辑。

在许多嵌入式系统应用场景里,分立式逻辑器件,如74'HC系列,被广泛使用。这些逻辑器件具备独立于单片机(MCU)工作的优势,其响应速度相较于软件而言要快得多。然而,它们也存在明显的弊端,那就是会增加物料清单(BOM)的成本,并且需要占用额外的PCB面积,这在对成本和空间要求严格的设计中是一大难题。

为了克服这些问题,Microchip的不少单片机都集成了相关外设。在PIC®MCU上集成了名为可配置逻辑单元(CLC)的外设,在AVR®MCU上则有类似的可配置定制逻辑(CCL)外设。这两种外设都能实现软件定义的定制逻辑,并且可以独立于CPU执行。也就是说,一旦定制逻辑功能设置完成,其运行就不再依赖于单片机。但它们也存在一定的局限性,每个实例可实现的逻辑数量较少。每个CLC大约等同于一个查找表(LUT),而CCL相当于一个内部有几个独立LUT的实例。虽然这两种外设功能强大,可用于开发简单逻辑电路、混合各种信号以及与其他硬件外设集成,像硬件按钮去抖、WS2812输出生成和正交解码等应用都能用到它们,但单片机中这两种外设的数量有限,限制了应用的复杂程度。

为了支持更复杂的应用需求,PIC16F13145系列单片机引入了一种新型逻辑外设——可配置逻辑模块(CLB),但需要注意的是,CLB并不会取代CLC或CCL外设,器件可以同时配备CLC/CCL和CLB。

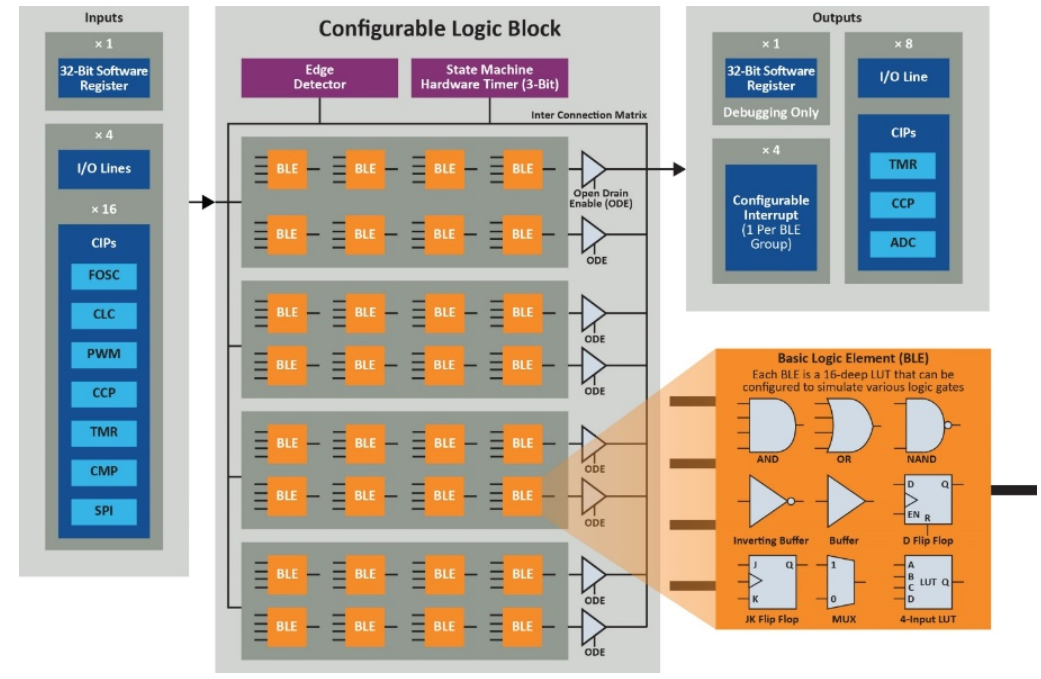

(图1——CLB框图)

PIC16F13145系列单片机上的CLB包含四个逻辑组,每组包含八个BLE。不同逻辑组的BLE之间相互连接,每个逻辑组对应两个GPIO输出和一个可选的CPU中断。当工作电压为5.5V时,BLE的传播时间典型值小于6ns。整个CLB结构中的所有BLE共用一个公共时钟,该时钟源可与可选的时钟分频器一起在软件中进行配置,CLB既可以使用单片机的内部时钟源,也能使用外部提供的时钟源。

该外设从单片机的存储器中进行初始化,之后可通过外设引脚选择(PPS)直接从自身结构中控制引脚。用户能够通过PPS重新分配用于硬件外设的I/O引脚,从而获得更大的设计灵活性。例如,如果SPI时钟原本使用RA1引脚,但使用RA6引脚在某些情况下更有利,那么就可以通过PPS重新映射引脚。

CLB中的其他元件还包括专用的3位硬件定时器(带解码输出)、用于输入信号的边沿检测器以及32位输出寄存器(用于调试)。单片机上其他独立于内核的外设(CIP)输出可以作为CLB的输入,以便实现更复杂的设计。

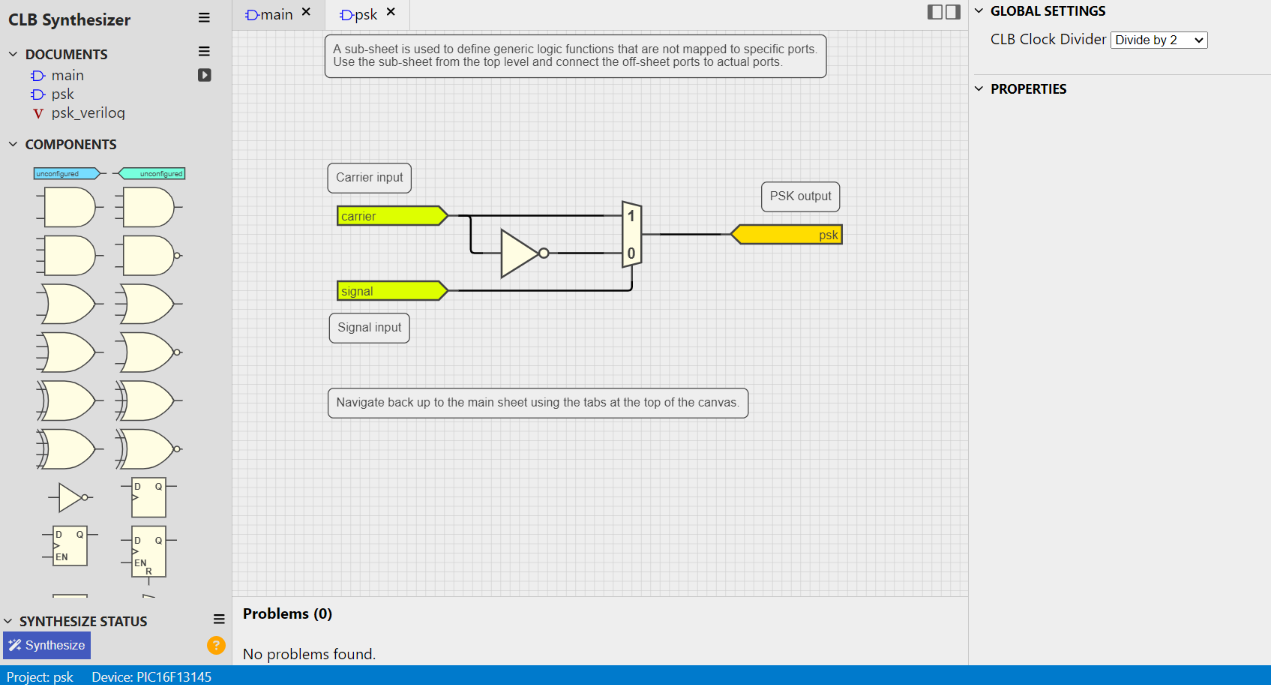

由于CLB比CLC或CCL复杂得多,Microchip专门开发了一款名为CLB合成器的新工具。CLB合成器提供了一个用于配置逻辑的图形界面,除了逻辑原语之外,该工具还支持更高级的逻辑模块库,这些模块库既可以由用户预先提供,也可以根据需求进行定制。

(图2——已打开相移键控(PSK)示例的CLB合成器)

与该图形工具交互时,后台会自动生成一个Verilog模块用于合成。如果开发人员更喜欢自己编写Verilog代码或者已经准备好了相关文件,也可以将其作为模块直接导入工具。CLB合成器的输出是一个汇编文件,其中包含用于设置CLB的比特流和一些用于将CLB配置为外设的源代码。该工具可以通过MPLAB^{®}代码配置器(MCC)或独立在线工具运行。MCC是一款代码生成实用程序,允许用户使用可视化界面来设置和配置单片机中的外设。当硬件外设完成配置后,MCC将生成初始化代码和器件API。

在运行时,使用板上硬件直接从程序存储器加载CLB比特流。这种实现方式的好处在于,如果在程序运行过程中需要更改CLB配置,就可以使用存储在器件存储器中的不同比特流重复执行加载过程。

为了更好地展示CLB的应用价值,我们创建了一系列用例示例,这里主要讨论两个典型示例:7段显示转换器和SPI至WS2812转换器。这些用例示例可以作为构件复制,用于构建完整解决方案的一部分。

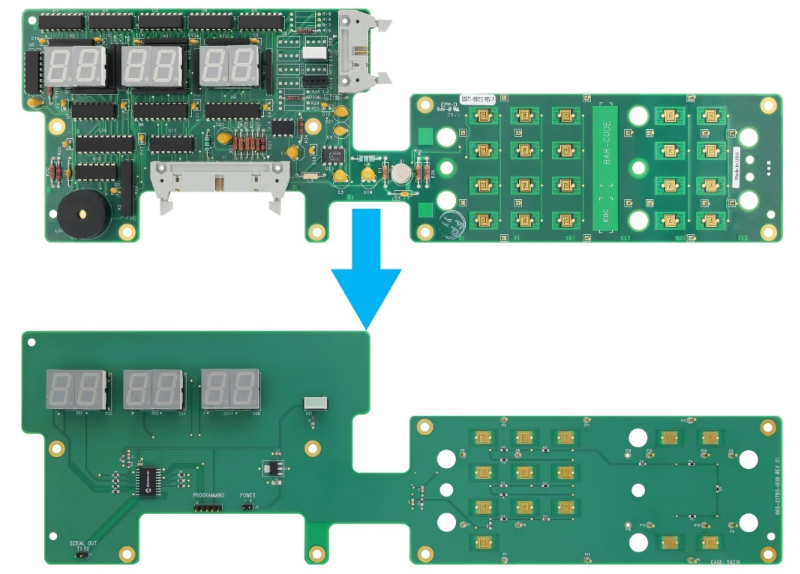

第一个用例是7段显示转换器。7段显示器通常可以通过一组普通的I/O引脚驱动,但标准实现一般需要使用软件定义的查找表,将输入数字转换为适合显示器的正确输出模式。而在这个实现中,CLB充当硬件查找表。所需的输出字符(0到F)从软件加载到CLB输入寄存器中,显示器的每个输出段均由LUT控制,从而将输入映射到输出。该用例示例在内部被用于构建计时系统的新控制板。最初的用户界面是在20世纪80年代使用74'HC系列逻辑开发的,使用CLB后,一个20引脚的单片机就可以实现电路板上的显示和键盘逻辑,大大精简了物料清单(BOM)。从图3中可以清晰地看到两种方案的对比情况。

(图3——原PCB与新PCB的并排比较。该示例由JoshBooth开发)

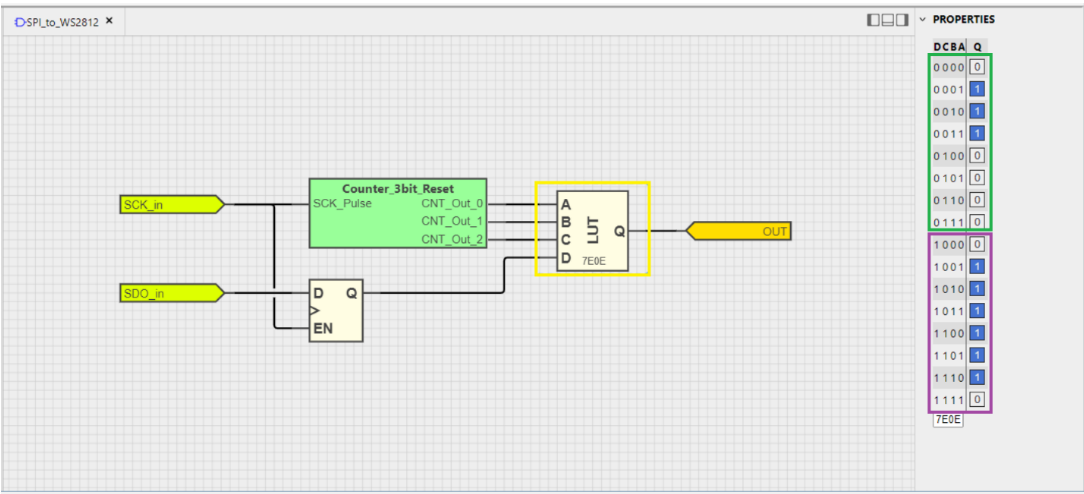

另一个示例是SPI至WS2812转换器。WS2812是一种单线串行协议,用于通过脉宽调制控制LED阵列。在这个例子中,SPI硬件作为要发送到LED的数据的移位寄存器,而CLB则用于将SCLK和SDO转换为预期的输出。具体来说,这是通过单触发3位计数器、带使能功能的D锁存器和4输入LUT来实现的,具体情况如图4所示。该实现的关键在于SPI和CLB的时钟源设置。SPI时钟设置为空闲高电平、在上升沿改变状态,并以WS2812输出的频率(800kHz)运行,而CLB的时钟源频率是SPI时钟的10倍(8MHz)。当SCLK为低电平时,将触发3位计数器并开始计数。当计数到7(0b111)时,3位计数器将停止并保持为0,直到时钟脉冲的下一个低电平周期为止。计数器的输出与输出数据的锁存版本一起馈入4输入LUT,以此来设置数据的输出模式。计数器复位后,计数器输出将保持为0以完成循环。之后,可根据需要发送SPI硬件中的下一个字节,重复该循环。

(图4——SPI至WS2812转换器框图(由PetreTeodor-Emilian开发))

这两个示例充分证明了单片机内部分立逻辑的显著优势。硬件外设能够将CPU从各种任务中解放出来,不仅可以缩短响应时间、降低功耗,还能减少元器件数量。有了CLB之后,以往无法在单片机内部实现的复杂应用现在都能够顺利开发。目前,开发人员可前往Microchip直销网站或其他代理商处购买PIC16F13145系列单片机来获取CLB功能,开启更高效、更灵活的嵌入式系统设计之旅。

759

759

浙公网安备 33010502006866号

浙公网安备 33010502006866号