74HCT377是一款八位D型触发器,具有数据使能功能,并且是正边沿触发的集成电路。这款芯片由Philips Semiconductors生产,广泛应用于需要地址寄存器和数据同步的场合。本文将对74HCT377的主要特性、电气特性和应用进行详细解读。

产品特性

地址寄存器应用的理想选择

数据使能用于地址和数据同步

八个正边沿触发的D型触发器

具有标准输出能力

属于MSI(中等规模集成电路)类别

一般描述

74HCT377是高速Si-gate CMOS设备,与低功耗肖特基TTL(LSTTL)引脚兼容。它们符合JEDEC标准号7A。该设备包含八个边沿触发的D型触发器,每个触发器都有单独的D输入和Q输出。当数据使能(E)输入为低电平时,公共时钟(CP)输入会同时加载所有触发器。每个D输入的状态会在低至高时钟转换前的一个设定时间被传输到相应的触发器输出(Qn)。

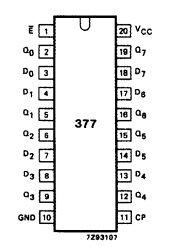

引脚描述

1号引脚(E):数据使能输入(低电平有效)

2、5、6、9、12、15、16、19号引脚(Q0到Q7):触发器输出

3、4、7、8、13、14、17、18号引脚(D0到D7):数据输入

10号引脚(GND):地(0V)

11号引脚(CP):时钟输入(低至高边沿触发)

20号引脚(VCC):正电源电压

功能表

功能表展示了在不同输入条件下触发器的输出状态。输入包括时钟(CP)、数据使能(E)和数据输入(Dn)。输出(Qn)的状态取决于CP的低至高边沿转换时Dn的电平。

操作模式

74HCT377的操作模式包括:

加载“1”:在CP的低至高边沿转换时,如果Dn为高电平,则Qn将被加载为高电平。

加载“0”:在CP的低至高边沿转换时,如果Dn为低电平,则Qn将被加载为低电平。

保持(无操作):在CP的低至高边沿转换时,如果E为高电平,则Qn保持当前状态不变。

电气特性

传播延迟(tPHL/tPLH):CP到Qn的传播延迟在不同温度和电源电压下的典型值和最大值。

输出转换时间(tTHL/tTLH):输出从低到高或从高到低的转换时间。

时钟脉冲宽度(tW):时钟脉冲的高或低宽度。

设定时间(tsu):数据输入(Dn)和数据使能(E)到CP的设定时间。

保持时间(th):数据输入(Dn)和数据使能(E)到CP的保持时间。

最大时钟频率(fmax):触发器能够正常工作的最大时钟频率。

应用电路

74HCT377可用于各种数字电路设计,特别是在需要数据存储和同步的应用中。例如,它可以用于微控制器的地址和数据寄存器,或者在数据通信系统中同步数据流。

结论

74HCT377是一款功能强大、灵活的八位D型触发器,适用于多种数字逻辑应用。通过详细解读其技术手册,设计工程师可以更好地利用这款芯片,实现高效、可靠的电路设计。Philips Semiconductors提供的详细技术数据和应用指南,为工程师提供了宝贵的设计参考。

浙公网安备 33010502006866号

浙公网安备 33010502006866号