Dual 16-Bit, 105 MSPS, 1.8 V

Analog-to-Digital Converter

AD9650-EP

Data Sheet

FEATURES

FUNCTIONAL BLOCK DIAGRAM

SDIO/ SCLK/

Dual 16-bit ADC in enhanced package for extended

temperature range of −55°C to +85°C

1.8 V analog supply operation

AVDD

CSB

DRVDD

DCS

DFS

SPI

AD9650-EP

LVDS output

OR+

SNR: 80.5 dBFS at 30 MHz input and 105 MSPS data rate

SFDR: 93 dBc at 30 MHz input and 105 MSPS data rate

Low power: 328 mW per channel at 105 MSPS

Integer 1-to-8 input clock divider

PROGRAMMING DATA

CMOS/LVDS

D15+ (MSB)

TO

D0+ (LSB)

VIN+A

VIN–A

16

ADC

OUTPUT BUFFER

CLK+

CLK–

IF sampling frequencies up to 300 MHz

Analog input range of 2.7 V p-p

DIVIDE 1

TO 8

VREF

SENSE

DCO+

DCO–

Optional on-chip dither

DUTY CYCLE

STABILIZER

DCO

GENERATION

REF

SELECT

Integrated ADC sample-and-hold inputs

Differential analog inputs with 500 MHz bandwidth

ADC clock duty cycle stabilizer (DCS)

VCM

RBIAS

VIN–B

VIN+B

OR–

D15– (MSB)

TO

D0– (LSB)

16

CMOS/LVDS

OUTPUT BUFFER

ADC

APPLICATIONS

Radar

MULTICHIP

SYNC

Electronic warfare (EW) systems

Joint tactical radio system (JTRS) and other COMSEC

Industrial instrumentation

AGND

SYNC

PDWN

OEB

NOTES

X-ray, MRI, and ultrasound equipment

High speed pulse acquisition

Chemical and spectrum analysis

General-purpose software radios

1. PIN NAMES ARE FOR THE LVDS PIN CONFIGURATION ONLY.

Figure 1.

GENERAL DESCRIPTION

The AD9650-EP is a dual 16-bit, 105 MSPS analog-to-digital

converter (ADC) designed for digitizing high frequency, wide

dynamic range signals with input frequencies of up to 300 MHz.

Additional application and technical information can be found

in the AD9650 data sheet.

PRODUCT HIGHLIGHTS

The dual ADC core features a multistage differential pipelined

architecture with integrated output error correction logic. Each

ADC features wide bandwidth, differential sample-and-hold analog

input amplifiers, and a shared integrated voltage reference, which

eases design considerations. A duty cycle stabilizer (DCS) is pro-

vided to compensate for variations in the ADC clock duty cycle,

allowing the converters to maintain excellent performance.

1. On-chip dither option for improved SFDR performance

with low power analog input.

2. Proprietary differential input that maintains excellent SNR

performance for input frequencies up to 300 MHz.

3. Operation from a single 1.8 V supply with a separate digital

output driver supply that accommodates 1.8 V CMOS or

LVDS outputs.

The ADC output data can be routed directly to the two external

16-bit output ports or multiplexed on a single 16-bit bus. These

outputs can be set to either 1.8 V CMOS or LVDS.

4. Standard serial port interface (SPI) that supports various

product features and functions such as data formatting

(offset binary, twos complement, or Gray coding), enabling

the clock DCS, power-down, and test modes.

5. 12 mm × 12 mm, 80-lead TQFP with an exposed pad

(7.5 mm × 7.5 mm).

Flexible power-down options allow significant power savings,

when desired. Programming for setup and control is accomplished

using a 3-wire, SPI-compatible serial interface.

The AD9650-EP is available in an 80-lead TQFP and is specified

over the extended temperature range of −55°C to +85°C.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rightsof third parties that may result fromits use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks andregisteredtrademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Technical Support

©2013 Analog Devices, Inc. All rights reserved.

www.analog.com

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

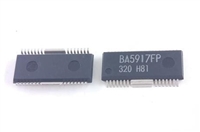

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐