| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 72T3695L6-7BBG | IDT |

获取价格 |

FIFO, 32KX36, 3.8ns, Synchronous, CMOS, PBGA208, 17 X 17 MM, 1 MM PITCH, GREEN, PLASTIC, B |

|

| 72T3695L6-7BBGI | IDT |

获取价格 |

2.5 VOLT HIGH-SPEED TeraSync FIFO 36-BIT CONFIGURATIONS |

|

| 72T40108L10BBG | IDT |

获取价格 |

FIFO, 64KX40, 4.5ns, Synchronous, CMOS, PBGA208, 17 X 17 MM, 1 MM PITCH, GREEN, PLASTIC, B |

|

| 72T40108L4BB | IDT |

获取价格 |

PBGA-208, Tray |

|

| 72T40108L4BBG | IDT |

获取价格 |

FIFO, 64KX40, 3.2ns, Synchronous, CMOS, PBGA208, 17 X 17 MM, 1 MM PITCH, GREEN, PLASTIC, B |

|

| 72T40108L5BB | IDT |

获取价格 |

PBGA-208, Tray |

|

| 72T40108L5BBG | IDT |

获取价格 |

FIFO, 64KX40, 3.6ns, Synchronous, CMOS, PBGA208, 17 X 17 MM, 1 MM PITCH, GREEN, PLASTIC, B |

|

| 72T40108L6-7BB | IDT |

获取价格 |

PBGA-208, Tray |

|

| 72T40108L6-7BBG | IDT |

获取价格 |

FIFO, 64KX40, 3.8ns, Synchronous, CMOS, PBGA208, 17 X 17 MM, 1 MM PITCH, GREEN, PLASTIC, B |

|

| 72T40108L6-7BBGI | IDT |

获取价格 |

FIFO, 64KX40, 3.8ns, Synchronous, CMOS, PBGA208, 17 X 17 MM, 1 MM PITCH, GREEN, PLASTIC, B |

|

国产x86处理器里程碑!兆芯6000台医疗电脑中标某总医院

国产x86处理器里程碑!兆芯6000台医疗电脑中标某总医院

稚晖君团队开源GO-1模型:ViLLA架构如何重塑具身智能未来?

稚晖君团队开源GO-1模型:ViLLA架构如何重塑具身智能未来?

安森美收购奥拉半导体Vcore技术 抢占AI数据中心电源管理制高点

安森美收购奥拉半导体Vcore技术 抢占AI数据中心电源管理制高点

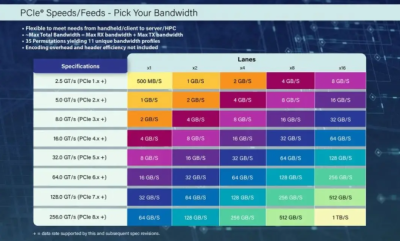

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代

PCIe 8.0规范草案获里程碑进展:256GT/s速率开启1TB/s带宽时代